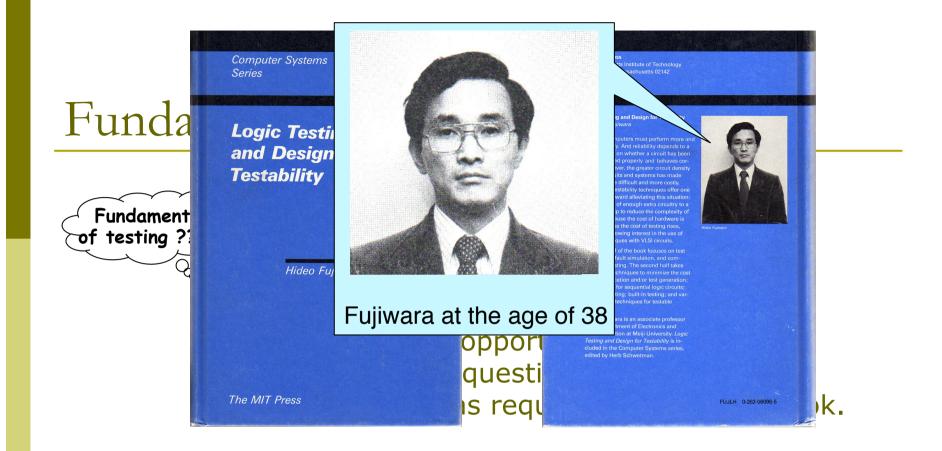

### Logic Testing and Design for Testability

MIT Press, Sept. 1985

Hideo Fujiwara

### The basis is necessary for development

- For a tree to grow larger, its root must grow bigger and deeper into the ground.

- Similarly, for test technologies (leaves) to develop, substantial results of the fundamental research (root) are necessary.

- The more enriched the fundamental research results become, the more enriched the practical research results become.

### Fundamental problems of testing

What are the fundamentals of testing?

I had the opportunity to ask myself the same question when I was requested to write a book.

To educate the fundamentals of testing, I wrote a book. Hideo Fujiwara, *Logic Testing and Design for Testability*, The MIT Press, 1985

To educate the fundamentals of testing, I wrote a book. Hideo Fujiwara, *Logic Testing and Design for Testability*, The MIT Press, 1985

### Fundamental problems of testing

- Test generation problem

- ATPG (Automatic Test Program Generation)

- Design-for-test problem

DFT

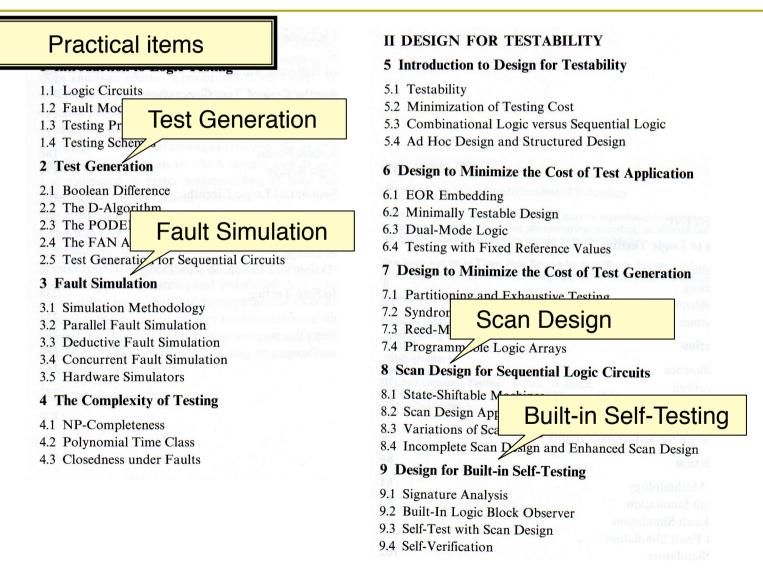

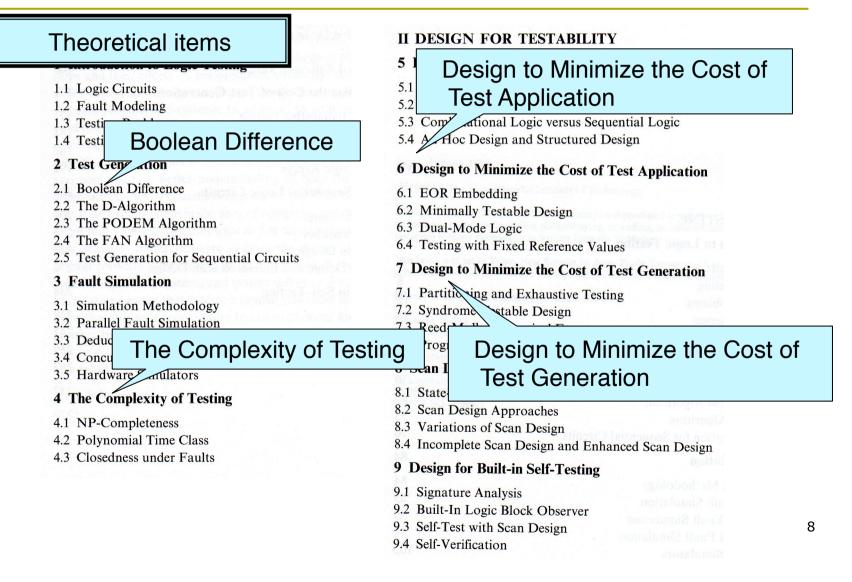

### H. Fujiwara, Logic Testing and Design for Testability, MIT Press, 1985

#### I LOGIC TESTING

#### 1 Introduction to Logic Testing

- 1.1 Logic Circuits

- 1.2 Fault Modeling

- 1.3 Testing Problems

- 1.4 Testing Schemes

#### **2** Test Generation

- 2.1 Boolean Difference

- 2.2 The D-Algorithm

- 2.3 The PODEM Algorithm

- 2.4 The FAN Algorithm

- 2.5 Test Generation for Sequential Circuits

#### **3** Fault Simulation

- 3.1 Simulation Methodology

- 3.2 Parallel Fault Simulation

- 3.3 Deductive Fault Simulation

- 3.4 Concurrent Fault Simulation

- 3.5 Hardware Simulators

#### 4 The Complexity of Testing

- 4.1 NP-Completeness

- 4.2 Polynomial Time Class

- 4.3 Closedness under Faults

#### **II DESIGN FOR TESTABILITY**

#### 5 Introduction to Design for Testability

- 5.1 Testability

- 5.2 Minimization of Testing Cost

- 5.3 Combinational Logic versus Sequential Logic

- 5.4 Ad Hoc Design and Structured Design

#### 6 Design to Minimize the Cost of Test Application

- 6.1 EOR Embedding

- 6.2 Minimally Testable Design

- 6.3 Dual-Mode Logic

- 6.4 Testing with Fixed Reference Values

#### 7 Design to Minimize the Cost of Test Generation

- 7.1 Partitioning and Exhaustive Testing

- 7.2 Syndrome-Testable Design

- 7.3 Reed-Muller Canonical Forms

- 7.4 Programmable Logic Arrays

#### 8 Scan Design for Sequential Logic Circuits

- 8.1 State-Shiftable Machines

- 8.2 Scan Design Approaches

- 8.3 Variations of Scan Design

- 8.4 Incomplete Scan Design and Enhanced Scan Design

#### 9 Design for Built-in Self-Testing

- 9.1 Signature Analysis

- 9.2 Built-In Logic Block Observer

- 9.3 Self-Test with Scan Design

- 9.4 Self-Verification

### H. Fujiwara, Logic Testing and Design for Testability, MIT Press, 1985

### H. Fujiwara, Logic Testing and Design for Testability, MIT Press, 1985

### Fundamental problems of testing

Practical synthesis problems

- Test generation algorithms.

- Invent efficient algorithms to provide high fault efficiency.

- Design-for-testability methods.

- Optimize the DFT under various constraints.

### Theoretical analysis problems

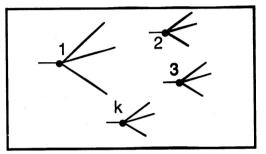

- Analysis of test generation complexity.

- Clarify the complexity of test generation algorithms.

- Classification of sequential circuits.

- Class of combinational test generation complexity.

- Class of acyclic test generation complexity.

Theory is the mother of practice Necessity is the mother of invention Theoretical research / fundamental research are necessary for practical research. Theoretical research Practical ideas FAN algorithm Polynomial Time Class ??? Analysis of test generation complexity Efficient ATPG Optimal design for testability Classification of sequential circuits

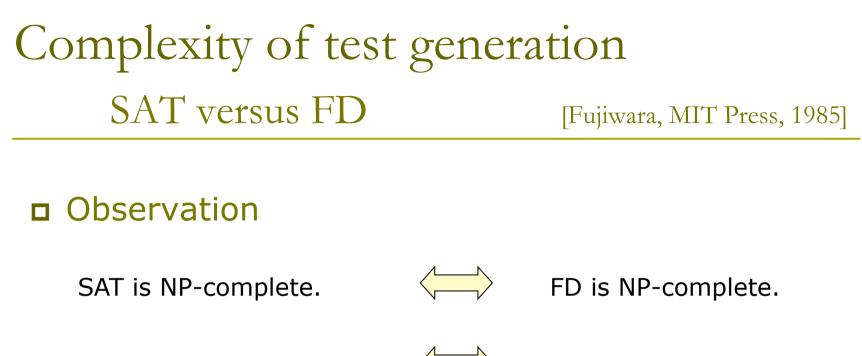

# Complexity of test generation

NP-completeness

[Fujiwara, MIT Press, 1985]

- A Boolean expression is *satisfiable* iff there exists some assignment of zeros and ones to the variables that gives the expression the value 1.

- **SAT (Satisfiability):** Is a Boolean expression satisfiable?

- **Theorem 1** [Cook 1971]: SAT is NP-complete.

- **U-SAT:** Satisfiability problem for *unate* expression

- Theorem 2 [Fujiwara 1982]: U-SAT is solvable in time O(L) where L is the length of an expression.

## Complexity of test generation

NP-completeness

[Fujiwara, MIT Press, 1985]

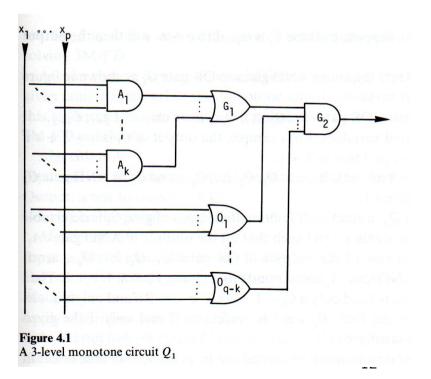

Fault detection (FD): Is a given single stuck-at fault detectable? kM-FD: Fault detection problem for k-level monotone circuits kU-FD: Fault detection problem for k-level unate circuits

Theorem 3 [Fujiwara 1982]: 3M-FD is NP-complete. Hence, 3U-FD and FD are NP-complete.

U-SAT is solvable in O(L).

U-FD is NP-complete.

M-SAT is solvable in O(L). M-FD is NP-complete.

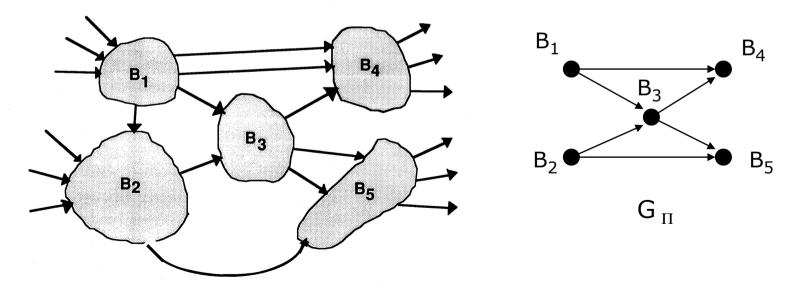

(1) the number of inputs of each block Bi is at most k, and (2) graph G  $_{\Pi}$  has no cycle.

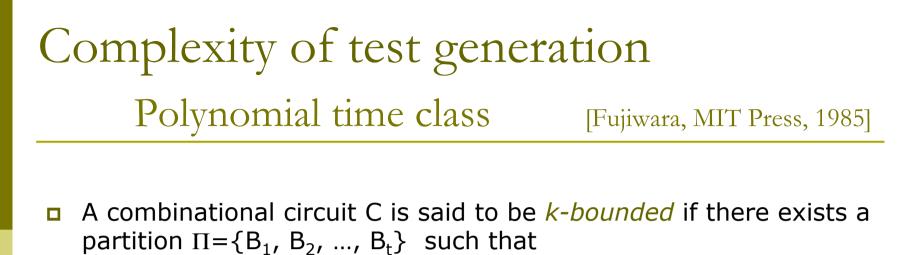

Complexity of test generation

k-bounded circuits

[Fujiwara, MIT Press, 1985]

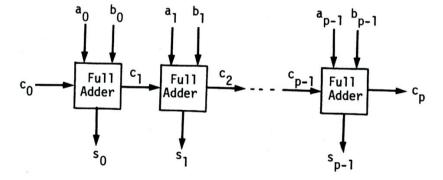

Theorem 4 [Fujiwara 1982]: Let C be a k-bounded circuit. Then there is an algorithm of time complexity O(16<sup>k</sup>m) to find a test for a single stuck-at fault in C, where m is the number of lines in C.

Figure 4.3 Ripple-carry adder

#### 3-bounded circuit

Figure 4.4 Gate-minimum *p*-bit adder

6-bounded circuit

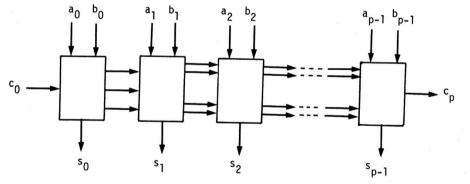

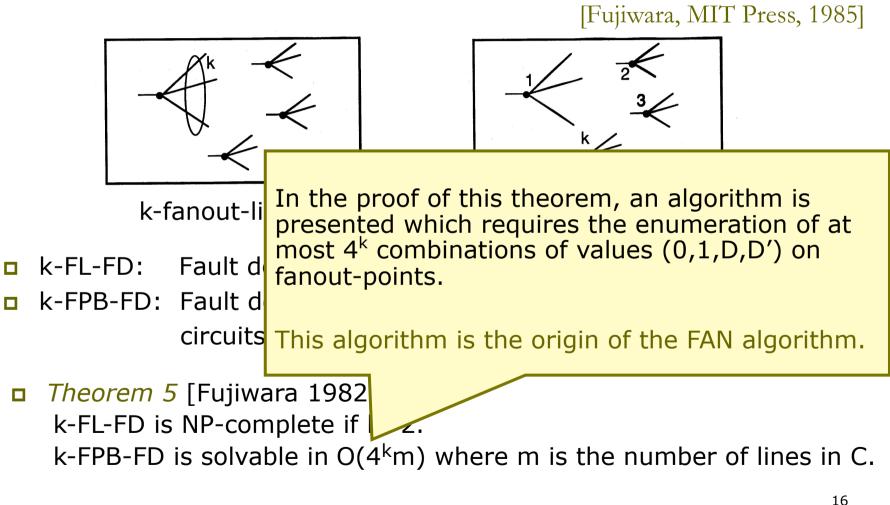

## Complexity of test generation

k-fanout-limited vs. k-fanout-point-bounded

# Complexity of test generation k-fanout-limited vs. k-fanout-point-bounded

k-fanout-limited

[Fujiwara, MIT Press, 1985]

k-fanout-point-bounded

Observation:

k-FL-FD is NP-complete even if k is a constant. k-FPB-FD is solvable in O(m) if k is a constant.

The complexity of test generation is affected

not by the number of fanout branches from a fanout point

but by the number of fanout points.

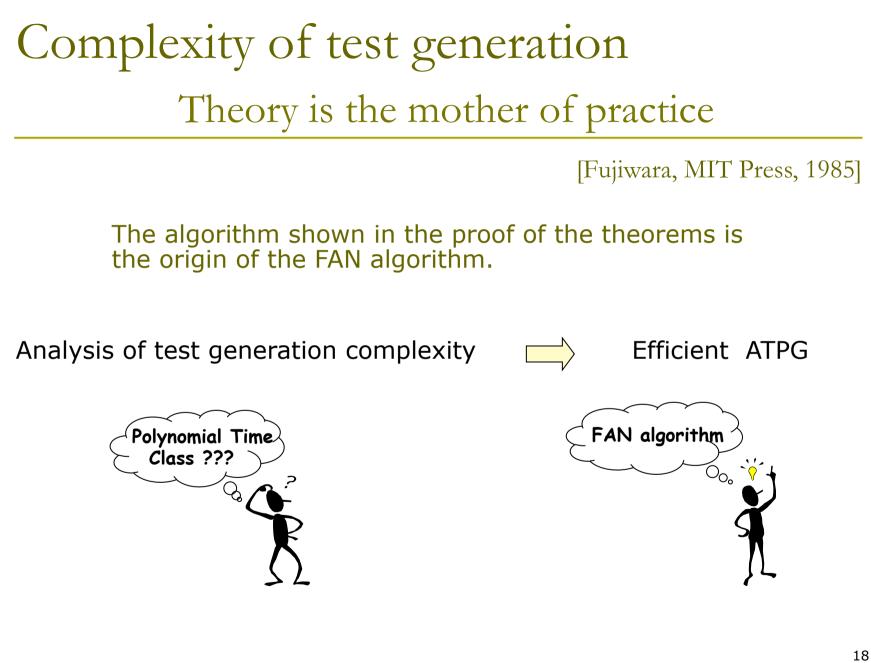

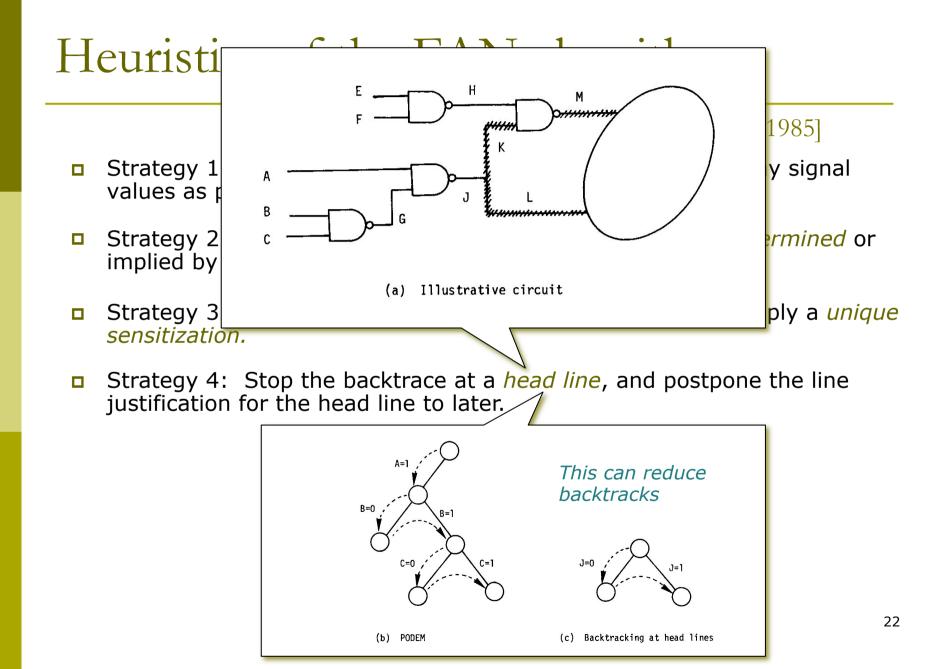

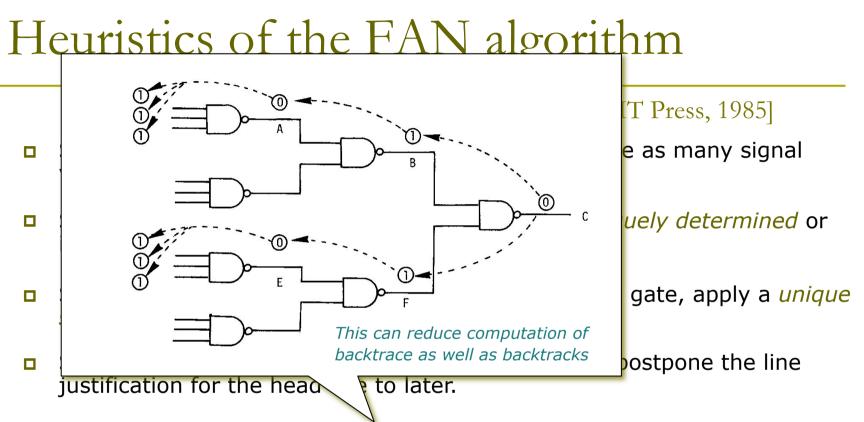

## Heuristics of the FAN algorithm

[Fujiwara, MIT Press, 1985]

Strategy 1: In each step of the algorithm, determine as many signal values as possible that can be *uniquely implied*.

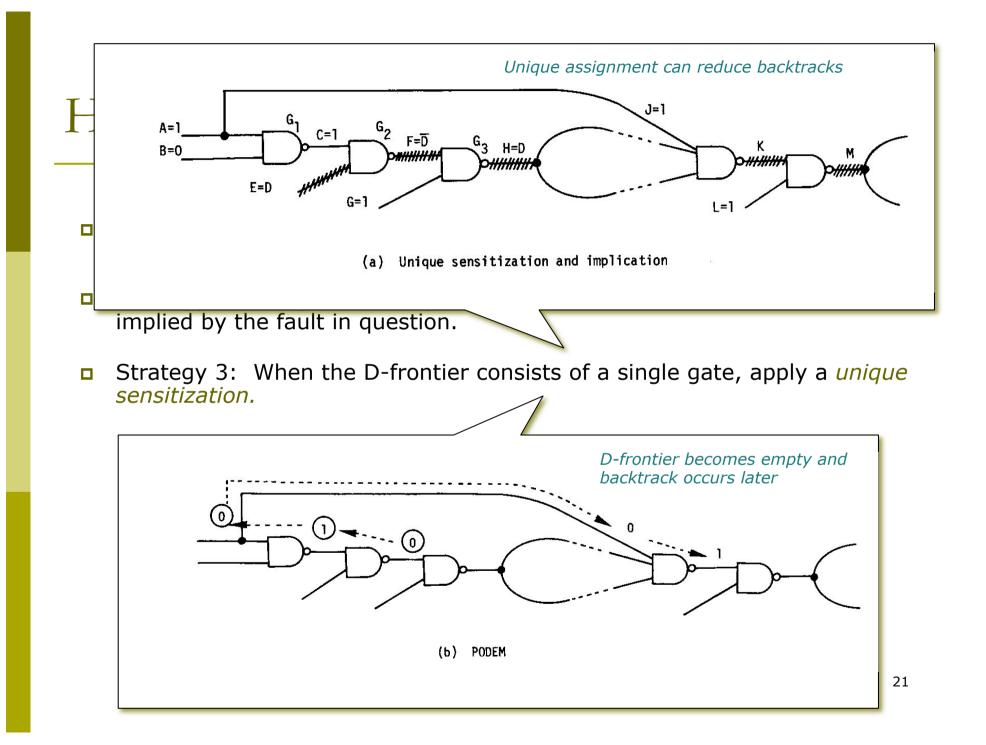

## Heuristics of the FAN algorithm

#### [Fujiwara, MIT Press, 1985]

- Strategy 1: In each step of the algorithm, determine as many signal values as possible that can be *uniquely implied*.

- Strategy 2: Assign a fault signal D or D' that is uniquely determined or implied by the fault in question.

Strategy 5: Multiple backtracing (concurrent backtracing of more than one path) is more efficient than backtracing along a single path.

## Heuristics of the FAN algorithm

Se

S

D

[Fujiwara, MIT Press, 1985]

- Strategy 1: In each step of the algorithm, determine as many signal values as possible that can be *uniquely implied*.

- Si

*PODEM* assigns a binary value only to primary inputs. So, backtracks occur at primary inputs.

Si

- *FAN assigns a binary value only to head lines and fanout points. So, backtracks occur at headlines and fanout points.*

This is effective to reduce the number of backtracks.

Strategy 6: In the multiple backtrace, if an objective at a fanout point p has a contradictory requirement, stop the backtrace so as to assign a binary value to the fanout point.

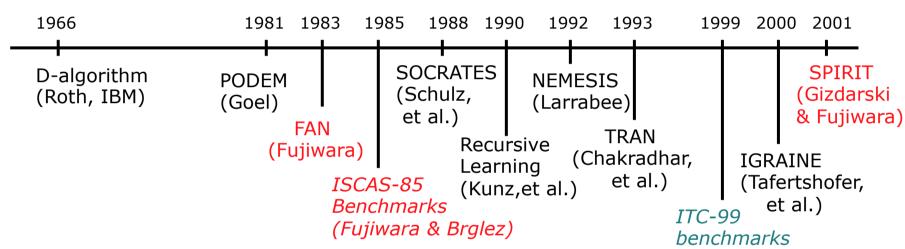

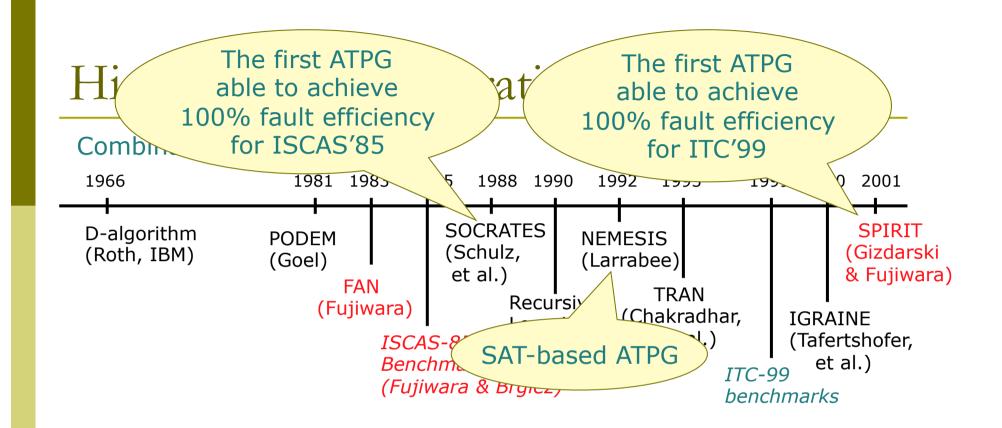

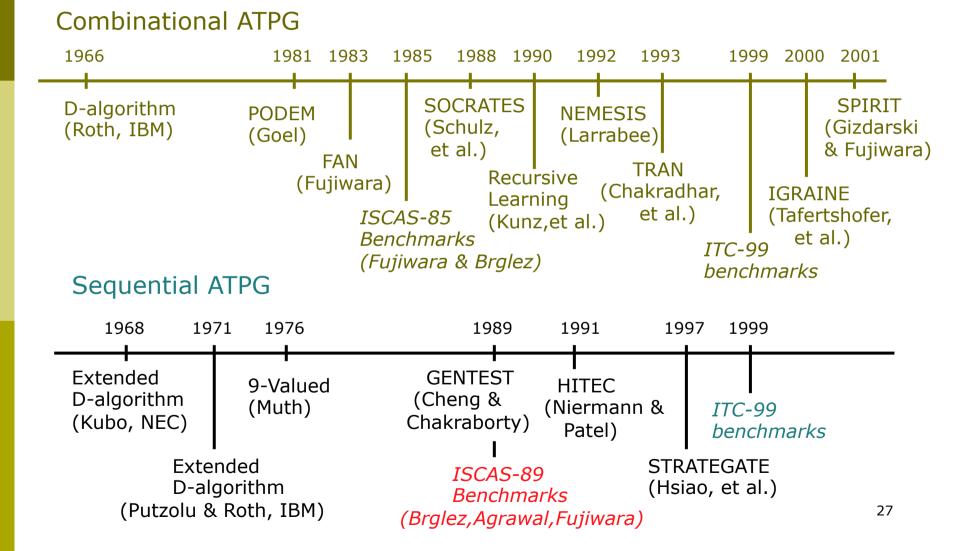

### History of test generation algorithms

#### Combinational ATPG

### History of test generation algorithms

#### Hideo Fujiwara, Logic Testing and Design for Testability, The MIT Press, 1985

https://mitpress.mit.edu/index.php?q=books/logic-testing-and-design-testability

# Thank you