# A Class of Sequential Circuits with Combinational Test Generation **Complexity under Single-Fault Assumption**

Michiko Inoue<sup>1</sup> Emil Gizdarski<sup>1,2</sup> Hideo Fujiwara<sup>1</sup>

1 Graduate School of Information Science, Nara Institute of Science and Technology 8916-5 Takayama, Ikoma, Nara, 630-0101 Japan

2 Department of Computer Systems, University of Rousse Rousse, 7017 Blugaria

#### Abstract

We show that the test generation problem for all single stuck-at faults in sequential circuits with internally balanced structures is reduced into the test generation problem for single stuck-at faults in combinational circuits. In our previous work, we introduced internally balanced structures as a class of sequential circuits with the combinational test generation complexity. However, single stuck-at faults on some primary inputs, called separable primary inputs, corresponded to multiple stuckat faults in a transformed combinational circuit. In this paper, we resolve this problem. We show how to generate a test sequence and identify redundancy for single stuckat faults on separable primary inputs.

### 1. Introduction

Test generation for sequential circuits is, in general, a difficult and intractable task which may be unsolvable within a reasonable time for a large-scale circuit[1,2]. When all the flip-flops of a circuit are replaced with scan flip-flops (full scan design), all the scan flip-flops are treated as equivalents to external I/O terminals and hence the test generation can be performed for the remaining circuit (called the "kernel circuit") with the exclusion of all flip-flops, i.e., for the combinational part of the sequential circuit. Therefore, the full scan design method can reduce the test generation problem for a sequential circuit to the problem of test generation for a combinational circuit. We shall consider only stuck-at faults in this paper, and refer stuck-at faults to hereafter just as faults.

To reduce area and delay overhead while preserving the above good feature of the full scan design, a class of sequential circuits that allows test generation with combinational test generation algorithms has been investigated[3]-[7]. Balanced structures[4] are one class of circuit structures with this feature. A sequential circuit is a balanced structure if it is acyclic and, for any pair of primary input and primary output, all paths between them have the same number of flip-flops. For a balanced sequential circuit, test generation problem can be reduced into the test generation problem for a combinational circuit obtained by replacing all flip-flops with wires. In this transformation, all single faults on a balanced circuit correspond to single faults on the transformed

combinational circuit. In [5], a sub-class of balanced structure called strongly balanced structures is introduced to reduce test application time. In [6], a balanced structure is considered at register-transfer level. At this level, the functional behavior of the combinational logic such as "switch" can be considered, and switched balanced structures are introduced as a larger class of the balanced structures. For an acyclic structure, test generation method that uses combinational test generation algorithm for a *time expansion model* is proposed[7]. Although this model allows test generation with combinational test generation algorithm, it includes multiple copies of the combinational blocks of the original sequential circuits. Therefore, the transformed circuits is much larger than the original circuit, and moreover, a test generation algorithm for *multiple* faults is needed. In [3], we introduced a new class of sequential circuits with combinational test generation complexity called internally balanced structure. This class is larger than the class of balanced structures. However, when considering realization possibility of finite state machines (FSMs), it is shown that {FSMs which can be realized as a sequential circuit of acyclic structure $\} = \{FSMs which can be realized as a$ sequential circuit of internally balanced structure}  $\supset$ {FSMs which can be realized as a sequential circuit of balanced structure}. We reduced the test generation problem for faults in a circuit S with an internally balanced structure into the test generation problem for faults in a combinational circuit C where some primary inputs with fanout branches in S are separated into two or more primary inputs according to some partition of the fanout branches. We call such primary inputs in S separable primary inputs. Each single fault on a separable primary input in S corresponds to a *multiple* fault on all the separated primary inputs in C, while the other single faults in S correspond to single faults in C.

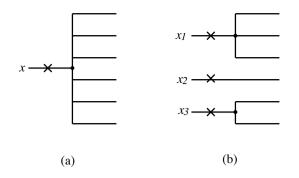

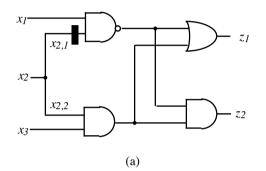

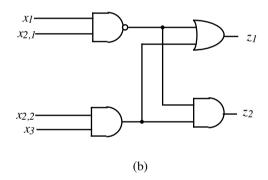

Figure 1 shows an example. The original circuits S has a separable primary input x (Fig.1(a)), and it is separated into three primary inputs  $x_1$ ,  $x_2$ ,  $x_3$  in the transformed circuit C (Fig1(b)). In such transformation, the fault on xin S corresponds to a multiple faults on  $x_1$ ,  $x_2$ ,  $x_3$  in C. Therefore, we needed a test generation algorithm for multiple faults to find test sequences for single faults on separable primary inputs.

Figure 1. Correspondence of faults: (a)A separable primary input in S, (b)separated primary inputs in C.

In this paper, we first show that test sequences corresponding to test patterns for single faults on separated primary inputs do not always detect faults on the separable primary inputs. This means that even if we can find test patterns for all detectable faults on the separated primary inputs of a primary input x, test sequences corresponding to these test patterns may not detect the fault on x though it is detectable.

We then present how to find test sequences for single faults on the separable primary inputs. We show that we can get a test sequence for a single stuck-at-v fault on a separable primary input directly from a test pattern for a single stuck-at-v fault on one of the separated primary inputs. We also show that a single stuck-at-v fault on a separable primary input is redundant if all single stuck-at-vfaults on the separated primary inputs are redundant. In this way, we reduce the test generation problem for single faults in circuits with internally balanced structures into the test generation problem for *single* faults in combinational circuits.

The rest of this paper in organized as follows. In Section 2 the internally balanced structure and some notations are provided. We show that faults on the separable primary inputs may not be detected by test sequences for the separated primary inputs, and show how to generate complete test sequences and identify redundancy in Section 3. Section 4 concludes the paper.

# 2. Preliminaries

First, we briefly define the internally balanced structure[3]. For simplicity, we shall limit flip-flops (referred to hereafter as FFs) to DFFs. Another kind of FFs can be handled similarly.

The number of FFs included in a path is called the sequential depth of the path. The largest sequential depth over the paths from the primary inputs of a sequential circuit to a primary output is regarded as the sequential depth of the primary output. The largest sequential depth over the primary outputs is regarded as the sequential depth of the sequential circuit. Suppose x is a primary input with fanout branches, and  $y_i$  and  $y_j$  are branches of x. If there is no primary output that can be reached from  $y_i$  and  $y_j$  over equal depth paths, then  $y_i$  and  $y_j$  are called *separable*.

**Extended Combinational Transformation:** A transformation based on the following two operations with a sequential circuit *S* of acyclic structure is called the extended combinational transformation ( $C^*$ -transformation), and the resulting combinational circuit is denoted by  $C^*(S)$ .

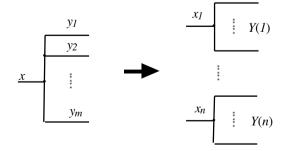

- (1) Separation of primary inputs: For each primary input x with fanout branches, *separate* it as follows. Let Y denote a set of the fanout branches of a primary input. Let us obtain the smallest partition  $\Pi$  of Y which satisfies the following statement: If branches  $y_a$  and  $y_b$  belong to different blocks Y(i), Y(j) of partition  $\Pi$  ( $y_a \in Y(i)$ ,  $y_b \in Y(j)$ ,  $Y(i) \neq Y(j)$ ) then  $y_a$  and  $y_b$  are separable. As shown in Fig.2, each partitioned block Y(i) is provided with a new primary input  $x_i$  separated from the original primary input x.

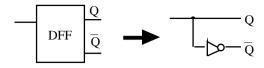

- (2) C-transformation: Replace each FF by a wire (for the case of negative FF output, a NOT gate is added, see Fig.3).

Note that we can uniquely obtain the smallest partition  $\Pi$  for each primary input as connected components of a graph such that the vertices are the fanout branches and an edge exists iff two fanout branches are not separable. In this way, for a given acyclic circuit *S*, the resulting circuit from the operation (1) of the *C*\*-transformation and the resulting circuit from the *C*\*-transformation are uniquely determined. Let *S*\*(*S*) and *C*\*(*S*) denote these circuits, respectively.

**Balanced Structure**[4]: For any pair of primary input and primary output in an acyclic circuit *S*, if the sequential depths of all paths connecting these two points are equal, then *S* is regarded as a *balanced structure*.

**Internally Balanced Structure**[3]: An acyclic circuit S is regarded as an *internally balanced structure* if a circuit  $S^*(S)$  is a balanced structure.

Figure 2. Primary input separation.

Figure 3. Deletion of flip-flops.

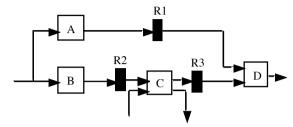

Figure 4. Example of internally balanced structure.

The circuit shown in Fig.4 is an internally balanced structure but is not a balanced structure where *A*, *B*, *C*, *D* are blocks of combinational logics and *R1*, *R2*, *R3* are registers (collections of FFs). On the other hand, if the circuit is balanced structure then it is also internally balanced structure. The relation among the structures is as follows: {sequential circuits with acyclic structure}  $\supset$  {sequential circuits with internally balanced structure}  $\supset$  {sequential circuits with balanced structure}.

Let *S* be a circuit with an internally balanced structure. We consider transformation of a test sequence *T* for *S* into a test pattern for  $C^*(S)$ . Let *z* be a primary output in both *S* and  $C^*(S)$ . We define transformation  $T_c(T, S, z, \tau)$  of a test sequence *T* for *S* into a test pattern for  $C^*(S)$  that determines the value of *z* in time frame  $\tau$  as follows. Assume that the length of *T* and  $\tau$  is more than the sequential depth of *z*. In the following, if there is no path from a primary input *x* to *z* in  $C^*(S)$ , we consider the value of *x* as *don't care*.

(1) Case where x is not a primary input in S separated in C\*(S):

The sequential depth *d* of any path from *x* to *z* is uniquely determined. The value of *x* in  $T_c(T, S, z, \tau)$ is the value of *x* of *T* in time frame  $\tau - d$ .

(2) Case where x is a primary input in S separated in C\*(S):

Assume that the primary input x in S is separated to obtain the primary inputs  $x_1, x_2, \dots, x_n$  in  $C^*(S)$ . Since S is an internally balanced structure, any path from  $x_j$  to z has unique sequential depth  $d_j$ . The value of  $x_j$   $(j=1, 2, \dots, n)$  of test pattern  $T_c(T, S, z, \tau)$  is the value of x of T in time frames  $\tau - d_j$   $(j=1, 2, \dots, n)$ .

In the second case, since all sequential depths  $d_j$  (j=1, 2,..., n) are different and the values of  $x_j$  (j=1, 2,..., n) determine the values of x of T in different time frames.

Therefore, we can define a test sequence T from a test pattern t satisfying  $t=T_c(T, S, z, \tau)$ .

In [3], we showed that the test generation problem for a sequential circuits S with internally balanced structure can be reduced to the test generation problem for a combinational circuit  $C^*(S)$ .

**Theorem 1[3]** If a sequential circuit S is an internally balanced structure, S allows test generation with combinational test generation complexity.

However, each fault on a separable primary input x in S corresponds to a multiple fault on all the separated primary inputs of x in  $C^*(S)$ . On the other hand, any other single fault f in S corresponds to a single fault f' on the same line in  $C^*(S)$ , and a test pattern t detects f' iff any test sequence satisfying  $t = T_c(T, S, z, d)$  detects f in S where t propagates a fault effect to a primary output z with a sequential depth d.

# 3. Detection of Separable Primary Input Faults

In this section, we consider whether the test generation problem for *single* faults in sequential circuits with internally balanced structures can be reduced to the test generation problem for *single* faults in combinational circuits. We first consider the following conjecture.

**Conjecture 1** Let *S* be a sequential circuit with internally balanced structure. The following statement holds for any primary input *x* in *S* which is separated into  $x_1, x_2, \dots, x_n$  in  $C^*(S)$ : If  $\{t_1, t_2, \dots, t_k\} \neq \emptyset$  is a complete test set for the single stuck-at-*v* faults on  $x_1, x_2, \dots, x_n$  in  $C^*(S)$  then there exists a test pattern  $t \in \{t_1, t_2, \dots, t_k\}$  such that any test sequences *T* satisfying  $t = T_c(T, S, z, d)$  detects a stuck-at-*v* fault on *x* in *S* where *t* propagates a fault effect to a primary output *z* and *d* is a sequential depth of *z* in *S*.

If the conjecture holds, we can generate a test sequence T for a single stuck-at-v fault on a separable primary input x as follows: First generate test patterns for single stuck-at-v faults on the separated primary inputs  $x_1, x_2, \dots, x_n$ , then transform them to test sequences for S. One of the test sequences can detect a stuck-at-v fault on x. In this way, we do not have to consider multiple faults in  $C^*(S)$ . However, the conjecture does not hold.

Theorem 2 Conjecture 1 does not holds.

*Proof*: Consider the sequential circuit S in Fig.5(a), where S is an internally balanced structure and a primary input  $x_2$  is separable. We can obtain a circuit  $C^*(S)$  in Fig.5(b) where  $x_2$  is separated into  $x_{2,1}$  and  $x_{2,2}$ . To prove the theorem, it is sufficient to show that, for each  $x_{2,j}$  (j=1,2), there is a test pattern t such that it detects a single stuck-

at-*v* fault on  $x_{2,j}$  and some sequence *T* satisfying  $t=T_c(T,S,z,d)$  cannot detect a stuck-at-*v* fault on  $x_2$  where *t* propagate a fault effect to a primary output *z* and *d* is the sequential depth of *z* in *S*.

Now, we show such test patterns for stuck-at-1 faults on  $x_{2,I}$  and  $x_{2,2}$ . Test pattern  $t=(x_I=1, x_{2,I}=0, x_{2,2}=0, x_{3}=1)$  can detect both stuck-at-1 faults on  $x_{2,I}$  and  $x_{2,2}$  in  $C^*(S)$ . It propagates D to  $z_I$  for a fault on  $x_{2,I}$  and  $\overline{D}$  to  $z_2$  for a fault on  $x_{2,2}$ . Both sequential depths of  $z_I$  and  $z_2$  are I, and a sequence T=000,101 satisfies  $t=T_c(T, S, z_I, I)$  and  $t=T_c(T, S, z_2, I)$  but does not detect a stuck-at-1 fault on  $x_2$ .

Figure 5. (a) Internally balanced structure S, (b) Combinational equivalent  $C^*(S)$ .

Although Conjecture 1 does not hold, we can find a test sequence which detects a fault on a separable primary input. For an input pattern  $t=(v_1, v_2, \dots, v_m)$  for a combinational circuit with primary inputs  $x_1, x_2, \dots, x_m$ , let  $t[x_i:=w_i, x_i:=w_j, \dots]$  denote the input pattern obtained from replacing the values of  $x_i, x_j, \dots$  with the values  $w_i, w_j, \dots$ .

**Theorem 3** Let *S* be a sequential circuit with internally balanced structure, where a primary input *x* in *S* is separated into  $x_1, x_2, \dots, x_n$  in  $C^*(S)$ . If *t* is a test pattern for a single stuck-at-*v* fault  $f_j$  on some  $x_j$  in  $C^*(S)$ , then a single stuck-at-*v* fault *f* on *x* in *S* can be detected by any *T* satisfying  $t=T_c(T, S, z, d)$  or any *T* satisfying  $t[x_j:=$

v]= $T_c(T', S, z, d)$  where z is the primary output to which t propagates a fault effect and d is the sequential depth of z in S.

*Proof*: Since t detects  $f_j$ , the value of  $x_j$  in t must be v. Let  $F(x_1, x_2, \dots, x_n, X)$  be a function of z in  $C^*(S)$ , where X is a list of primary inputs other than  $x_1, x_2, \dots, x_n$ . Without loss of the generality, we assume that t propagates a value D to z in  $C^*(S)$ . As a result, the following holds.

$$F(t) = 1$$

$F(t[x_j:=v]) = 0$

Let  $F^*(T,\tau)$  denote the value of z in a time frame  $\tau$  on applying an input sequence T to S. Since S is an internally balanced structure,  $F^*(T,d) = F(T_c(T, S, z, d))$ holds. Let  $F_f^*(T,d)$  denote the value of z in a time frame d on applying an input sequence T to S with a fault f.

(1) Case of  $F(t) \neq F(t[x_1:=v, \cdots, x_n:=v])$ :

Let *T* be any sequence satisfying  $t=T_c(T, S, z, d)$ . In this case the following holds.

$$F^{*}(T,d) = F(T_{c}(T, S, z, d))$$

=  $F(t)$

$$F_{f}^{*}(T,d) = F(t[x_{1}:=v, \cdots, x_{n}:=v])$$

$$\neq F(t)$$

Therefore, f can be detected by any T.

- (2) Case of  $F(t) = F(t[x_1 := v, \dots, x_n := v])$ :

- Let *T*' be any sequence satisfying  $t[x_j = v] = T_c(T', S, z, d)$ . In this case the following holds.

$$F^{*}(T',d) = F(t[x_{j}:=v])$$

= 0

$$F_{f}^{*}(T',d) = F(t[x_{1}:=v,\cdots,x_{n}:=v])$$

= F(t)

= 1

Therefore, f can be detected by any T'.

Let  $T_{S,x,v}$  denote a set of test sequences (or test patterns) that detect a stuck-at-v on a line x in S. Assume that a primary input x is separated into primary inputs  $x_1$ ,  $x_2, \dots, x_n$  in  $C^*(S)$ . Theorem 3 implies that

$\bigcup_{1 \le j \le n} T_{C^*(S), \chi j, \nu} \neq \emptyset \Rightarrow T_{S, \chi, \nu} \neq \emptyset \text{ holds. We now show}$  $\bigcup_{1 \le j \le n} T_{C^*(S), \chi j, \nu} = \emptyset \Rightarrow T_{S, \chi, \nu} = \emptyset.$

**Theorem 4** Let *S* be a circuit with an internally balanced structure, where a primary input *x* is separated into  $x_1, x_2$ ,  $\cdots$ ,  $x_n$  in  $C^*(S)$ . Then,  $\bigcup_{1 \le j \le n} T_{C^*(S), xj, v} = \phi \Rightarrow T_{S, x, v} = \phi$  holds.

*Proof*: We prove the theorem by contradiction. Assume 4 -

$\bigcup_{1 \le j \le n} T_{C^*(S), xj, v} = \emptyset$  but  $T_{S, x, v} \ne \emptyset$ . Let *T* be a test sequence that detects a stuck-at-*v* fault *f* on *x* in *S* where *T* propagates an error to an output *z* in a time frame  $\tau$ . Let *F* be a function of *z* in *C*\*(*S*). Since any stuck-at-*v* fault *f<sub>j</sub>* on *x<sub>j</sub>* is redundant,  $F(t)=F(t[x_j:=0])=F(t[x_j:=1])=F(t[x_j:=v])$  holds for any *x<sub>j</sub>* and any input pattern *t*.

Since the primary input x in S is separated into  $x_I$ ,  $x_2, \dots, x_n$  in  $C^*(S)$  and T is a test sequence for f,  $F(T_c(T, S, z, \tau)) \neq F(T_c(T, S, z, \tau)[x_I:=v, \dots, x_n:=v])$  holds. However, the following also holds.

$$F(T_c(T, S, z, \tau))$$

=  $F(T_c(T, S, z, \tau)[x_1 := v])$

=  $F(T_c(T, S, z, \tau)[x_1 := v, x_2 := v])$

...

=  $F(T_c(T, S, z, \tau)[x_1 := v, \cdots, x_n := v])$

The contradiction occurs.

Using the result in [3] and Theorems 3 and 4, we can generate a test sequence for single faults in an internally balanced circuit S using a test generation algorithm for single faults in a combinational circuit. The procedure to generate a test sequence is as follows.

- 1. Transform S into a combinational circuit  $C^*(S)$ .

- 2. Generate test patterns for all single faults in  $C^*(S)$  using a combinational test generation algorithm.

- 3. For all faults except on the separated primary inputs in *C*. Transform each test pattern *t* into a test sequence *T* so as to satisfy  $t=T_c(T, S, z, d)$  where *t* propagates a fault effect to a primary output *z* and *d* is the sequential depth of *z* in *S*. If a fault *f* is identified as redundant in  $C^*(S)$ , identify the same fault in S as redundant. Concatenate all obtained test sequences. Let T be a concatenated sequence.

- 4. For each stuck-at-v fault on each separable primary input x in S, if some separated primary input  $x_j$ separated from x has a test pattern t for a stuck-at-v fault, then append a test sequence T satisfying  $t=T_c(T, S, z, d)$  and a test sequence T' satisfying  $t[x_j:=v]=T_c(T', S, z, d)$  to T where z is the primary output to which t propagates a fault effect and d is the sequential depth of z in S. Otherwise, identify a stuck-at-v fault on x as redundant.

If a complete test generation algorithm for combinational circuits is available, the above procedure provides complete test sequence T for the internally balanced circuit S. Note that the 4th step in the above procedure may add two test sequences for one single fault. Theorem 3 guarantees that one of the two sequences can detect the fault. Therefore, we can delete one of them from T using a fault simulator to reduce the length of a test sequence.

#### 4. Conclusions

In this paper, we considered the test generation problem for the single stuck-at-v faults on the separable primary inputs of a sequential circuit with an internally balanced structure. We first showed that test sequences corresponding to test patterns for single stuck-at-v faults on the separated primary inputs  $x_1, x_2, \cdots, x_n$  cannot always detect the single stuck-at-v fault on x. However, we showed that a single stuck-at-v fault on x can be detected if one of the stuck-at-v faults on the separated primary inputs is detected. We presented how to find a test sequence for the fault on x using a test pattern for any of the separated primary inputs. We also showed that if any single stuck-at-v fault on the separated primary inputs is redundant then a single stuck-at-v fault on x is also redundant. As a result, the test generation problem for single faults on separable primary inputs in a sequential circuit with an internally balanced structure can be reduced to the test generation problem for single faults in a combinational circuit.

In [3], it is shown that the test generation problem for single faults on all lines except for the separable primary inputs of a sequential circuit with an internally balanced structure can be reduced to the test generation problem for single faults in a combinational circuit. As a result, the test generation problem for *all* single faults in a sequential circuit with an internally balanced structure is reduced to the test generation problem for single faults in a combinational circuit. We proposed the test generation procedure for internally balanced circuits. This procedure guarantees 100% fault efficiency if a complete test generation algorithm for single stuck-at faults in combinational circuits is available.

#### References

- [1] H. Fujiwara, *Logic Testing and Design for Testability*, The MIT Press, 1985.

- [2] M. Abramovici, M. A. Breuer, and A. D. Friedman, *Digital Systems Testing and Testable Design*, Computer Science Press, 1990.

- [3] H. Fujiwara, "A new definition and a new class of sequential circuits with combinational test generation complexity," in *Proc. 13th Intl. Conf. on VLSI Design*, pp.288-293, Jan. 2000.

- [4] R. Gupta, R. Gupta, and M. Breuer, "The BALLAST methodology for structured partial scan design," *IEEE Trans. on Computers*, vol.39, no.4, pp.538-544, April 1990.

- [5] A. Balakrishnan and S. T. Chakradhar, "Sequential circuits with combinational test generation complexity," in *Proc. 9th Intl. Conf. on VLSI Design*, pages 111-117, Jan. 1996.

- [6] R. Gupta and M. A. Breuer, "Partial scan design of register-tranfer level circuits," *Journal of Electronic Testing: Theory and Applications*, vol.7, pp.25-46, 1995.

- [7] T. Inoue, T. Hosokawa, T. Motohara, and H. Fujiwara, "An optimal time expansion model based on combinational ATPG for RT level circuits," in *Proc. 7th Asian Test Symposium*, pp.190-197, Dec. 1998.