# ホールドとスイッチの機能を考慮した内部平衡構造

Internally Balanced Structure with Hold and Switching Functions Chikateru JINNO<sup>†\*</sup>, Michiko INOUE<sup>†</sup>, and Hideo FUJIWARA<sup>†</sup>

あらまし 本論文では,ホールドとスイッチの機能を考慮して,内部平衡構造を拡張した順序回路のクラスである内部切換平衡構造を提案する.提案するクラスは,組合せテスト生成複雑度でテスト生成可能であり,平衡構造,内部平衡構造,切換平衡構造の順序回路のクラスを真に含む.本論文では,内部切換平衡構造順序回路に対して,(1)組合せ論理部の故障に対して組合せテスト生成複雑度でテスト生成可能であることを示し,(2)ホールドレジスタ及びスイッチの故障に対して検出可能となるための十分条件と故障検出率の実験的評価を示し,(3)計算量に基づく組合せテスト生成複雑度に関して考察する.

キーワード 平衡構造,内部平衡構造,切換平衡構造,組合せテスト生成複雑度,テスト生成

## 1. まえがき

順序回路のテスト生成は一般に困難な問題であり,回路規模が大きくなると実用的な時間で解けなくなる場合が多い[2].完全スキャン設計法では,スキャンレジスタを取り除いた残りの回路(核回路と呼ぶ)に対して組合せ回路用のテスト生成アルゴリズムが適用可能であるが,ハードウェアオーバヘッドは大きくなる.一方,部分スキャン設計法では,核回路にレジスタが残るため,一般には,順序回路用のテスト生成アルゴリズムを適用しなければならない.完全スキャン設計法の利点を保持したままハードウェアオーバヘッドを削減するために,組合せ回路用のテスト生成アルゴリズムでテスト生成が可能な順序回路のクラスが提案されている[1],[3]~[8].

平衡構造,内部平衡構造,切換平衡構造は,組合せ論理部に対し,組合せテスト生成複雑度でテスト生成可能[3]な順序回路のクラスである.レジスタとしてロードレジスタだけを考える場合,順序回路の回路構造には、{無閉路構造順序回路}⊃{内部平衡構造順序回路}~~( 平衡構造順序回路 }という関係がある.一

方,有限状態機械を実現可能性で分類すると{無閉路構造実現可能な有限状態機械}={内部平衡構造実現可能な有限状態機械}={内部平衡構造実現可能な有限状態機械}となる[3].文献[5]の平衡構造順序回路に関する定義では,レジスタとしてロードレジスタとホールドレジスタを考慮しているが,文献[3]の内部平衡構造順序回路に関する定義では,レジスタとしてロードレジスタだけを考慮している.

本論文では,内部平衡構造の定義がホールドレジス タを含むように拡張する.更に,切換平衡構造と同様 に,スイッチの機能を考慮して内部平衡構造を拡張し た内部切換平衡構造を提案する.内部切換平衡構造は, 組合せ論理部に対し、組合せテスト生成複雑度でテス ト生成可能な順序回路のクラスであり,平衡構造[5], 内部平衡構造 [3], 切換平衡構造 [4] を真に含むクラス である. 故障として信号線の縮退故障を考える. まず, 内部切換平衡構造順序回路が,ホールドレジスタの 制御信号線,スイッチ以外の故障に対し,組合せテス ト生成複雑度でテスト生成可能であることを示す.ま た,平衡構造[5],切換平衡構造[4]では考慮されてい なかったホールドレジスタの制御信号線,スイッチの 故障に対し,検出可能であるための十分条件を示す. 更に,この十分条件だけで,ホールドレジスタの制御 信号線,スイッチの故障に対し,高い故障検出率が得 られることを実験的に評価する.

本論文ではまず,拡張組合せ変換により順序回路の

<sup>†</sup> 奈良先端科学技術大学院大学情報科学研究科,生駒市

Graduate School of Information Science, Nara Institute of Science and Technology, 8916–5 Takayama-cho, Ikoma-shi, 630–0192 Japan

<sup>\*</sup> 現在,三菱電機株式会社

テスト生成問題が組合せ回路のテスト生成問題に帰着する回路を組合せテスト生成複雑度でテスト生成可能な順序回路と定義し議論する.5.では,更に,文献[3]で提案された計算量に基づく組合せテスト生成複雑度に関しても,組合せテスト生成複雑度でテスト生成可能であることを示す.

### 2. 内部切換平衡構造

## 2.1 諸 定 義

順序回路 S は I 組合せ論理部 I レジスタ I スイッチ からなる.組合せ論理部はレジスタ,スイッチ,外部入 力,外部入力の分岐枝に接続する連結した極大な組合 せ回路部分とする.レジスタには,ホールドレジスタ とロードレジスタがある.ホールドレジスタは,値を 保持するホールドモード(制御信号の値0)と,値を取 り込むロードモード(制御信号の値1)をもつ.ロー ドレジスタは常にロードモードで動作する.スイッチ は,マルチプレクサやバスである.レジスタ,スイッ チの制御信号及びクロック信号は,独立に外部から直 接印加されるとする.また,経路に含まれるレジスタ の個数をその経路の順序深度と呼ぶ.本論文では,組 合せテスト生成複雑度でテスト生成可能な順序回路の クラスとして無閉路順序回路を考える.以下,順序回 路として無閉路順序回路のみを考える.まず,分離可 能性を定義する.本論文では,文献[3]で定義された 分離可能性を拡張する.

[ 定義 1 ] (分離可能性 ) x を外部入力 ,  $y_i$  と  $y_j$  を x の分岐枝とし , z を  $y_i$  と  $y_j$  から到達可能な任意の 外部出力とする .  $y_i$  と  $y_j$  から z に至る任意の経路対 に対し , 一方の経路にのみ存在するホールドレジスタ が存在するか , または外部入力に最も近いホールドレジスタまたは外部出力までの順序深度が異なるならば ,  $y_i$  と  $y_j$  は分離可能という .

[定義 2 ](拡張組合せ変換) 以下の 2 操作を行う. ( 1 ) 外部入力分離: 外部入力 x の分岐枝の集合を Y とする. 分岐枝  $y_a$  と  $y_b$  が分割  $\Pi$  の異なるブロック Y(i) , Y(j) に属する  $(y_a \in Y(i)$  ,  $y_b \in Y(j)$ ;  $Y(i) \neq Y(j)$  ) ならば  $y_a$  と  $y_b$  は分離可能であるという条件を満たす Y の最小分割  $\Pi$  を求める. 分割した各ブロックごとに新たに外部入力を設けて , x を分離する.

(2) 組合せ変換:各レジスタを同じビット幅の信号線に置き換える.

順序回路 S に対し,外部入力分離操作のみ,及び拡

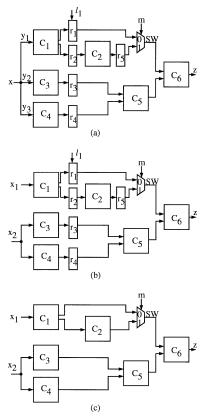

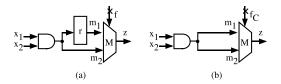

図 1 順序回路; (a) S (内部切換平衡構造), (b)  $S^*$  (切換平衡構造), (c)  $C^*(S)$

Fig. 1 Sequential circuits: (a) S (internally switched balanced structure), (b)  $S^*$  (switched balanced structure, (c)  $C^*(S)$ .

張組合せ変換を適用した結果の回路は一意に決まる.それらを,それぞれ  $S^*$ , $C^*(S)$  と表す(図 1). [ 定義 3 ] (組合せテスト生成複雑度でのテスト生成可能性 ) S を無閉路順序回路,f を S の故障とする. $C^*(S)$  に f に対応する故障  $f_C$  が存在し,f が S で検出可能であるための必要十分条件が  $f_C$  が  $C^*(S)$  で検出可能であるならば,S は f に対して,組合せテスト生成複雑度でテスト生成可能であるという.  $\Box$

#### 2.2 内部切換平衡構造

まず,トポロジーグラフと切換平衡構造を定義する. [定義 4] (順序回路 S に対するトポロジーグラフ)順序回路 S の組合せ論理部,スイッチ,外部入力,外部出力をそれぞれ頂点とし,頂点間の接続関係を有向辺とした有向グラフを S のトポロジーグラフという.トポロジーグラフの辺は信号線,ロードレジスタ,ホールドレジスタを表す.トポロジーグラフの経路に

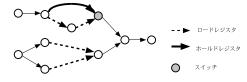

図 2 トポロジーグラフ Fig. 2 Topology graph.

含まれるロードレジスタ辺及びホールドレジスタ辺の個数を,その経路の順序深度と呼ぶ.  $\ \square$  図 2 に,図 1 (b)  $S^*$  のトポロジーグラフを示す. [ 定義 5 ] ( 切換平衡構造 ) 順序回路 S のトポロジーグラフ  $G_S$  に対し,以下が成り立つならば,S は切換平衡構造であるという.

- (1)  $G_S$  は無閉路である.

- (2) 任意の頂点対 u,v に対し , u から v へのすべての経路が , 順序深度が等しい , 若しくは頂点 u とは異なる同じスイッチ頂点 m を通過する .

- ( 3 ) 任意の頂点対 u,v に対し , u から v へのある経路上にホールドレジスタ h が存在するならば , u から v へのすべての経路が h を通過する , 若しくは u から v へのすべての経路が頂点 u とは異なる同じスイッチ頂点 m を通過する .

[定義 6] (内部切換平衡構造) 順序回路 S への外部 入力分離操作の結果得られる  $S^*$  が切換平衡構造であるならば , S は内部切換平衡構造であるという.  $\square$

図 1(a) の順序回路 S は, $S^*$ (図 1(b))が切換平衡構造となるので,内部切換平衡構造である.

## 3. 組合せテスト生成可能性

順序回路 S が内部切換平衡構造ならば,レジスタ及びスイッチのデータ入出力信号線,組合せ論理部,外部入力の故障に対し,S は組合せテスト生成複雑度でテスト生成可能であることを示す.ここで,S の故障 f は, $C^*(S)$  の同じ信号線に対する故障  $f_C$  に対応する.ただし,S の外部入力 x が  $C^*(S)$  で外部入力  $x_1,\cdots,x_m$  に分離した場合は,x の故障 f は, $x_1,\cdots,x_m$  の多重故障  $f_C$  に対応する.テストパターン  $T_C$  の入力 x の値を  $T_C(x)$ ,テスト系列 T の入力 x の時刻 t の値を T(x,t) と表す.

[補題 1] S を内部切換平衡構造順序回路とする .S のレジスタのデータ入出力信号線 , スイッチのデータ入出力信号線 , 組合せ論理部 , 外部入力の縮退故障 f が検出可能であるならば , f に対応する故障  $f_C$  は  $C^*(S)$  で検出可能である .

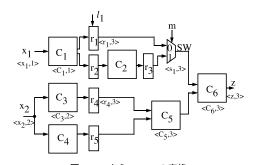

図 3 T から  $T_C$  への変換 Fig. 3 Transformation from T to  $T_C$ .

(証明) S における f のテスト系列 T を  $C^*(S)$  における  $f_C$  のテストパターン  $T_C$  に変換する .

T の長さを  $l_T$  とし,f は時刻  $l_T$  に外部出力 z に誤りを伝搬するとする. $C^*(S)$  の各外部入力 x に対して,T の x に対応する S の外部入力のどの時刻の値が,時刻  $l_T$  における z の値に影響するかを考える.この値が各 x に対して一意に決まれば,T におけるその時刻の値を割り当てることによって  $T_C$  を作ることができる.

S における時刻  $l_T$  の z の値に影響する時刻を  $S^*$  を用いて求める(図3参照). a を組合せ論理部,スイッチ,レジスタ,外部入力,及び外部出力とし,時刻  $t_a$  での a の出力値が時刻  $l_T$  における z の値に影響することを  $\langle a, t_a \rangle$  と表す.

$\langle z, l_T \rangle$  をキューに入れ,以下をすべての外部入力に 時刻が求まるまで繰り返す.

- (1) キューから一つの要素  $\langle a, t_a \rangle$  を取り出す.

- (2) a が外部入力でないとき,a の入力に接続する任意の組合せ論理部,スイッチ,レジスタ及び外部入力を a' とする.

- *a* がホールドレジスタの場合

時刻 t での a の制御信号線の値を  $c_t$  とする.時刻  $t_a$  での a の値をロードした時刻を t' とすると,  $t'=max\{t|(t< t_a)\wedge(c_t=1)\}$  となる.t' の値が決まらない場合, $t'=-\infty$  とする. $\langle a',t'\rangle$  をキューに入れる.

- $\bullet$  a がロードレジスタの場合  $\langle a', t_a 1 \rangle$  をキューに入れる .

- ullet a が組合せ論理部またはスイッチの場合  $\langle a',t_a

angle$  をキューに入れる .

a' がスイッチの場合,時刻  $t_a$  の制御信号線の値によって選択されない入力にのみ到達可能な部分回路を

削除する .S は内部切換平衡構造であり,また,スイッチは制御信号により選択された入力だけを考慮している.よって,再収斂する経路の順序深度は等しく,また,再収斂する経路のある経路にホールドレジスタ h が存在する場合,他のすべての経路にこの h が含まれる.これより,z から a' への複数の経路が存在しても  $\langle a',t'\rangle$  の値は一意に決まる.

$S^*$  の外部入力 x が S の外部入力 x' から分離したとする.外部入力 x に対し  $\langle x,t_x \rangle$  ならば ,  $T_C(x)=T(x',t_x)$  とする.スイッチ m に対し  $\langle m,t_m \rangle$  ならば , m の制御信号線  $c_m$  に対し ,  $T_C(c_m)=T(c_m,t_m)$  とする.時刻が決まっていない外部入力の値やスイッチの制御信号線の値は , ドント・ケアとする.

このようにして決まる  $T_C$  は, $C^*(S)$  における  $f_C$  を検出することがわかる.

以下の補題は,スイッチの故障も対象とする.

[補題 2 ] S を内部切換平衡構造順序回路とする  $C^*(S)$  のレジスタのデータ入出力信号線 , 組合せ論理部 , 外部入力 , スイッチの縮退故障  $f_C$  が検出可能であるならば ,  $f_C$  に対応する故障 f が S で検出可能である .

(証明)  $C^*(S)$  における  $f_C$  のテストパターン  $T_C$  をS における f のテスト系列 T に変換する .

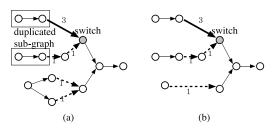

$f_C$  による誤りが外部出力 z に伝搬されるとする.  $S^*$  の z に対する出力錘において ,  $T_C$  によって各ス イッチで選択される経路だけを考えた部分回路に対す るトポロジーグラフを G' とする . ただし , 故障  $f_C$ がスイッチ m の故障の場合は , m のすべての入力を 考慮する.このとき,mの複数の入力に対して,それ らに到達可能なG'の部分グラフに共通部分があれば 複製し、それらが共通部分をもたないように修正した グラフを G' とする(図 4(a)). G' は切換平衡構造 のトポロジーグラフで,かつスイッチで再収斂する経 路をもたないので,頂点u,v間のある経路がホール ドレジスタをもたなければ,u,v間のすべての経路 はホールドレジスタを含まず,その順序深度は等しい。 頂点 u , v 間の経路を , その順序深度と同数のロード レジスタ辺からなる経路で置き換える.この操作を ホールドレジスタをもたない再収斂経路がなくなるま で繰り返したグラフを G とする(図 4(b)). G' は, 異なるロードレジスタ辺を通る再収斂経路をもたない ので,Gは木構造となる.

各レジスタ辺に z に誤りを伝搬させるために必要な値を何時間保持するかを表す重みを割り当てる.ロー

図 4  $T_C$  から T への変換:(a)G', (b)GFig. 4 Transformation from  $T_C$  to T; (a)G', (b)G.

ドレジスタの重みを1とする.ある経路上のすべてのレジスタの重みの和を経路重みという.以下,ホールドレジスタの重みを割り当てる.

外部入力から外部出力に至る経路で,ホールドレジスタ辺を含まな1 経路の最大の経路重みを  $d_{max}$  とする.なければ, $d_{max}=0$  とする.

外部入力から外部出力に至りホールドレジスタ辺を 含む経路に対し,経路に含まれるホールドレジスタ辺 の個数の昇順に,ホールドレジスタ辺の個数が等しい 場合は順序深度の昇順に,経路 P を選択し,以下を 行う.ホールドレジスタ辺の個数,順序深度がともに 等しい経路は任意の順序で選択する. P の経路重み  $W_P$  が ,  $W_P \ge d_{max} + 1$  となるように , 各ホールド レジスタ辺に1以上の重みを割り当てる.このとき, 経路上のホールドレジスタ辺の集合が等しい他の経路 の経路重みも同時に決まる.ここで,Gは木構造なの で、経路上のホールドレジスタ辺の集合が等しい経路 のみ同時に決まる.経路の選択順序より,これらはPと同数以上のロードレジスタ辺をもつので,経路重み は  $W_P$  以上となる .S の同一の外部入力から分離し た  $S^*$  の異なる外部入力を始点とする経路の経路重み が同時に決まる場合は,分離可能性の条件より,それ らは外部入力に最も近いホールドレジスタまでの順序 深度が異なるので経路重みは異なる.経路重みが決ま る経路の最大の経路重みを  $d_{max}$  とする.

すべての経路に対する経路重みが定まった時点での  $d_{max}$  に対し,テスト系列長  $l_T$  を  $l_T=d_{max}+1$  と する.G における頂点 v,辺 a の始点となる頂点から z に至る経路の経路重みをそれぞれ  $W_v$ , $W_a$  とする.G の外部入力頂点 x が, $C^*(S)$  の外部入力 x',S の外部入力 x'' に対応するとする. $T(x,''l_T-W_x)=T_C(x')$  とする.S の同一の外部入力から分離した  $S^*$  の異なる外部入力から z までの経路の経路重みは相異 なるので,衝突なく値を割り当てることができる.

G の各ホールドレジスタ辺 h の重みを w とする S の対応するホールドレジスタ r の制御信号を , 時刻  $(l_T-W_h)$  の値を 1 ,区間  $[l_T-W_h+1,l_T-W_h+w-1]$  の値を 0 に決める . ただし ,h が複製され ,同じ時刻に 0 と 1 の両方の値を割り当てようとする衝突が起きる場合は ,その時刻の値をドント・ケアとする . レジスタ r に値を取り込むのは ,r のデータ入力線の値が , $C^*(S)$  に  $T_C$  を印加した場合のその信号線の値 v となるときである . よって ,制御信号の値に衝突が起きる場合 ,データ入力線 ,レジスタの値がともに v となっているので制御信号線の値は 0 でも 1 でもよい .

スイッチ m の制御信号線を  $c_m$  とする .T での  $c_m$  の値を  $T_C(c_m)$  に固定する . それ以外の値はドント・ケアと決める .

以上のようにして決まる T は S における f を検出することがわかる .

[ 定理 1 ] S を内部切換平衡構造順序回路とする .S のレジスタ及びスイッチのデータ入出力信号線,組合せ論理部,外部入力の故障に対し,S は組合せテスト生成複雑度でテスト生成可能である .

(証明) 補題1と補題2より,成り立つ. □

S の分離する各外部入力 x に対する故障は,組合せ回路  $C^*(S)$  で x が分離した全外部入力に対する多重故障に対応する.文献 [6] では,組合せ回路の複数の外部入力の多重故障のテスト生成問題を,それら複数の外部入力に対する単一故障のテスト生成問題に帰着した.よって,内部切換平衡構造順序回路の組合せ論理部の単一故障に対するテスト生成問題は組合せ回路の単一故障のテスト生成問題に帰着する.

次に,スイッチの故障を検出するための十分条件(補題2)が必要条件ではないことを示す.

[補題 3] S を内部切換平衡構造順序回路とする .S のスイッチの故障 f が検出可能であるが .f に対応する故障  $f_C$  は  $C^*(S)$  で検出可能でないことがある .

(証明) 図 5 のスイッチ M の二つの入力を  $m_1$  ,  $m_2$  とする . 図 5 (a) では,テスト系列 T=(01,11) を  $x_1$  ,  $x_2$  に印加すれば,M に  $(m_1m_2)=(01)$  を印加することができ,M の制御信号線の縮退故障 f を検出できる.しかし,図 5 (b) の  $C^*(S)$  では,M に  $(m_1m_2)=(00),(11)$  のパターンしか印加することができず, $f_C$  を検出できない.

ホールドレジスタの故障に対して,検出可能である ための十分条件を示す.

[補題 4] S のホールドレジスタ h に対応する  $C^*(S)$

図 5 スイッチの故障 Fig. 5 Faults in a switch.

の信号線を i とする .  $C^*(S)$  において ,i の 0 縮退故障と 1 縮退故障がともに検出可能であるならば ,h の制御信号線の故障は検出可能である .

(証明) h の入力信号線,出力信号線をそれぞれ  $h_{\rm in}$ , $h_{\rm out}$  とする.補題 2 において,i のテストパターンを変換して得られた  $h_{\rm in}$  の 0 縮退故障,1 縮退故障のテスト系列を  $T_0$ , $T_1$  とする.このとき, $T_0$  は  $h_{\rm out}$  の 0 縮退故障のテスト系列でもある. $T_0$ , $T_1$  はそれぞれ長さが  $l_0$ , $l_1$  であり,外部出力  $z_0$ , $z_1$  に誤りを伝搬するとする.また, $T_0$  において時刻  $l_0$  の  $z_0$  の値に影響する  $h_{\rm in}$ , $h_{\rm out}$  の値の時刻を  $t_0$ , $t_0'$  とし, $t_0'$  において時刻  $l_1$  の  $t_0'$  の値の時刻を  $t_0$  た。

### (1) hの制御信号線の0縮退故障

故障時に h は常にホールドモードで動作するので,常にその初期値を出力する.これは,i の 0 縮退故障,または 1 縮退故障と等価とみなすことができるので, $T_0$  と  $T_1$  を印加することによって検出可能である.

### (2) hの制御信号線の1縮退故障

$T_0$  において,時刻  $t_0'$  の  $h_{

m out}$  の値が正常時と故障時で異なれば  $z_0$  で異なる出力を得ることができ,故障が検出可能となる.そこで,以下の場合に分けて考える.

- $T_0$  において時刻  $t_0'-1$  の  $h_{\rm in}$  の値が 0 の場合  $T_0$  は  $h_{\rm out}$  の 0 縮退故障のテスト系列であるので,正常時,時刻  $t_0'$  の  $h_{\rm out}$  の値を 1 とする.故障時,時刻  $t_0'-1$  の  $h_{\rm in}$  の値が 0 となるので,時刻  $t_0'$  の  $h_{\rm out}$  の値は 0 となる.

- $T_0$  において時刻  $t_0'-1$  の  $h_{\rm in}$  の値が 1 の場合  $T'=T_1T_0$  とし,T' の h の制御信号線の区間  $[t_1+1,l_1+t_0'-1]$  の値を 0 と変更したテスト系列を T とする. $T_1$  は  $h_{\rm in}$  の 1 縮退故障のテスト系列であるので,時刻  $t_1$  において h の値を 0 にする.正常時,時刻  $l_1+t_0'$  まで値は保持されるので,時刻  $l_1+t_0'$  の  $h_{\rm out}$  の値は 0 となる.故障時,時刻  $l_1+t_0'-1$  の  $h_{\rm in}$  の値が 0 となるので,時刻  $l_1+t_0'$  の  $h_{\rm out}$  の値は

1となる.

#### 4. 実験評価

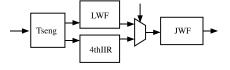

内部切換平衡構造順序回路  $S \, \succeq \, C^*(S)$  に対してテスト生成を行い,組合せ ATPG を使うことの効果を評価する.また,補題 2 , 4 で,ホールドレジスタの制御信号線,スイッチの故障に対して,検出可能であるための十分条件を示したが,この十分条件での故障検出率を実験的に評価する.実験には,ワークステーションとして Sun Blade 1000 を用いた.対象とする回路は,DP4 及び ISB-RISC である.DP4 は四つのベンチマーク回路 Tseng,4thIIR,LWF,JWF を図 6 のように接続した回路を,ISB-RISC は RISC のデータパス部を,それぞれ核回路が内部切換平衡構造となるように部分スキャン設計を行った結果の回路である.これら核回路の回路特性を表 1 に示す.

回路全体に対するテスト生成の結果を表 2 に示す . S は順序回路 DP4, ISB-RISC を表し ,  $C^*(S)$  は  $C^*(\mathrm{DP4})$  ,  $C^*(\mathrm{ISB-RISC})$  を表す .  $C^*(S)$  に対するテスト生成に対しては , その結果 S において検出

るが,S と比べてより多くの故障が検出可能または冗長と判定された.すなわち,組合せ ATPG を用いてテスト生成を行うことにより,より短いテスト生成時間で高い故障検出率,高い故障検出効率を得ることができた. 次に,ホールドレジスタの制御信号線の故障に対する結果を表 3 に示す.DP4 に対して, $C^*(S)$  を用いたテスト生成では 30 個中 28 個の故障が検出可能であった.S に対するテスト生成を行った結果,残りの 2 個の故障は冗長故障であることがわかった.また、ISB-RISC に対して, $C^*(S)$  を用いたテスト生成です

可能, 冗長, 判定不可能となる故障数も示す. DP4,

ISB-RISC に対し ,  $C^*(S)$  を用いたテスト生成では ,

S に比べ,より多くの故障が検出可能となり,テスト生成時間もそれぞれ約 1/10000,1/20 と大幅に短縮

した.また, $C^*(S)$ で判定不可能となる故障も存在す

る結果を表 3 に示す.DP4 に対して, $C^*(S)$  を用いたテスト生成では 30 個中 28 個の故障が検出可能であった.S に対するテスト生成を行った結果,残りの 2 個の故障は冗長故障であることがわかった.また, ISB-RISC に対して, $C^*(S)$  を用いたテスト生成ですべての故障が検出可能であった.最後に,スイッチの故障に対する結果を表 4 に示す.補題 1 と等価故障解析を行い,データ入出力信号線の故障及びその等価故障の冗長判定を行った.DP4 に対して, $C^*(S)$  を用いたテスト生成で S のすべての検出可能な故障が

図 6 回路 DP4 Fig. 6 Circuit DP4.

表 1 回路特性 Table 1 Circuit characteristics.

| 回路名      | ビット<br>幅 | PΙ   | РО   | ホールド<br>レジスタ | ロード<br>レジスタ | ゲート   |

|----------|----------|------|------|--------------|-------------|-------|

| DP4      | 16       | 320  | 304  | 15           | 12          | 24381 |

| ISB-RISC | 32       | 1088 | 1152 | 7            | 12          | 70248 |

表 3 ホールドレジスタの故障 Table 3 Faults in hold registers.

| 回路名      | 全故障数 | 検出故障 (C*(S)) | 冗長判定故障 (S) |

|----------|------|--------------|------------|

| DP4      | 30   | 28           | 2          |

| ISB-RISC | 14   | 14           | _          |

表 4 スイッチの故障 Table 4 Faults in switches.

| 回路名      |          | 故障数   |       |      |       |  |  |

|----------|----------|-------|-------|------|-------|--|--|

|          |          | 全故障   | 検出可能  | 冗長判定 | 判定打切り |  |  |

| DP4      | S        | 9214  | 9178  | 36   | 0     |  |  |

|          | $C^*(S)$ | 9214  | 9178  | 36   | 0     |  |  |

| ISB-RISC | S        | 38976 | 38756 | 207  | 13    |  |  |

|          | $C^*(S)$ | 38976 | 38756 | 220  | 0     |  |  |

表 2 テスト生成結果

Table 2 Test generation results.

| 回路名      |          | テスト生成時間 (s) | 全故障数   | 検出可能な故障数 |        | 冗長と判定された故障数 |      |       | 判定が打ち切られた |

|----------|----------|-------------|--------|----------|--------|-------------|------|-------|-----------|

|          |          |             |        | $C^*(S)$ | S      | $C^*(S)$    | S    |       | お障数       |

|          |          |             |        |          |        |             | 冗長   | 判定不可能 | HAPTAA    |

| DP4      | S        | 18476.9     | 30590  |          | 27404  |             | 361  |       | 2825      |

|          | $C^*(S)$ | 1.6         | 28640  | 25517    | 27461  | 3123        | 3115 | 14    | 0         |

| ISB-RISC | S        | 38251.2     | 120140 |          | 118984 |             | 272  |       | 884       |

|          | $C^*(S)$ | 1952.4      | 119358 | 119037   | 119789 | 235         | 137  | 128   | 86        |

検出できた.ISB-RISC に対しては, $C^*(S)$  を用いたテスト生成で検出できない故障は冗長であると判定できたが,S に対するテスト生成では一部の故障の判定が打ち切られるという結果となった.

#### 5. 計算量に基づく組合せテスト生成可能性

#### 5.1 計算量に関する定義

文献 [3] で定義された計算量に基づく組合せテスト生成複雑度でのテスト生成可能性に関して考察する.ここで,テスト生成問題として以下の問題を扱う.

$P_C$  (組合せテスト生成問題): 組合せ回路 C における故障 f を検出するテストパターンが存在するかを判定する問題で,インスタンスは組合せ回路 C と故障 f である.

$P_{\alpha}$  ( クラス  $\alpha$  テスト生成問題 ): クラス  $\alpha$  の順序回路 S における故障 f を検出するテスト系列が存在するかを判定する問題で,インスタンスはクラス  $\alpha$  の順序回路 S と故障 f である.

$T_C(n)$  と  $T_{\alpha}(n)$  をそれぞれテスト生成問題  $P_C$  と  $P_{\alpha}$  の計算量とする.ここで,n はその問題のインスタンスの大きさを表す.

[ 定義 7 ] ( 帰着可能性 ) 問題 A に属する任意のインスタンス a の解が , 問題 B に属する  $\tau(a)$  の解と同じとなる変換  $\tau$  が存在するならば , 問題 A は問題 B に帰着可能である .

[定義8](計算量に基づく組合せテスト生成複雑度でのテスト生成可能性)

以下を満たす変換 au が存在するならば , クラス lpha は組合せテスト生成複雑度でテスト生成可能であるという .

- (1)  $P_{\alpha}$  は変換  $\tau$  によって  $P_{\alpha}$  に帰着可能である.

- ( 2 )  $T_{\tau}$  を変換  $\tau$  に必要な計算量としたとき,順序回路のクラス  $\alpha$  に属する順序回路 S に対して, $T_{\tau}(S$  のサイズ) $=O(T_C(S)$  のサイズ)かつ  $T_C(\tau(S))$  のサイズ) $=O(T_C(S))$  が成り立つ.

組合せテスト生成複雑度でテスト生成可能な順序回路 S のテスト生成問題は,S を組合せ回路  $\tau(S)$  に変換し, $\tau(S)$  に組合せテスト生成アルゴリズムを適用することによって解くことができる.この全体の計算量は,組合せテスト生成問題の計算量( $=T_C(S)$  のサイズ))以下である.

組合せテスト生成問題  $P_C$  は NP 完全である.しかし,実際に設計される回路のクラスに対しては,経験的に,回路のサイズを n としたとき, $T_C=O(n^k)$ ( $k=2\sim3$ )といわれている.組合せテスト生

成複雑度でテスト生成可能な順序回路のクラスは, $T_C(n) = O(n^3)$  であると仮定し,以下考察する.

5.2 内部切換平衡構造の組合せテスト生成複雑度 S を内部切換平衡構造順序回路とする .S のサイズを n とすると  $,C^*(S)$  のサイズも n となり  $,T_C(C^*(S))$  のサイズ)  $=T_C(n)$  となる . よって , 拡張組合せ変換に必要な計算量を  $T_{C^*}(n)$  とすると  $,T_{C^*}(n)=T_C(n)$  であれば , 内部切換平衡構造順序回路のクラスは組合せテスト生成複雑度でテスト生成可能となる .

拡張組合せ変換の計算量  $T_{C^*}(n)$  は,外部入力分離操作,及び組合せ変換に必要な計算量となる.組合せ変換の計算量は O(n) である.外部入力分離操作は,外部入力の分岐枝集合の最小分割を求める操作であり,入力として分岐枝間の分離可能性が与えられていれば,分岐枝を頂点とし,分離可能でない頂点間を辺で接続したグラフのすべての連結成分を求める問題に帰着でき,計算量は  $O(n^2)$  である.よって, $T_{C^*}(n) = O(n^2)$  となる.

しかし,厳密には,テスト生成問題の入力に,分岐 枝間の分離可能性は含まれていない.以下,外部入力 分離操作を実現する一つの手続きを示し,その計算量 の上界を与える.外部入力の分岐枝の総数を  $n_f (\leq n)$ , 外部出力数を  $n_o (\leq n)$  とする.また,一つの経路上 に存在するロードレジスタ,ホールドレジスタ数の最 大値をそれぞれ  $n_l$ , $n_h (\leq n)$  とする.

(1) 各分岐枝からロードレジスタ,または外部出力 までの順序深度を求める . 経路 P に対し , P の始点に最 も近いホールドレジスタまたは終点を first(P), P の 始点から first(P) までの順序深度を  $first\_depth(P)$ と表す .S は無閉路順序回路であるので ,u ,v を始 点としホールドレジスタを含む二つの経路  $P_i$ ,  $P_j$  に 対し,  $first(P_i) \neq first(P_i)$  ならば, それらの経路 は一方にのみ存在するホールドレジスタをもつ.逆に,  $first(P_i) = first(P_i)$  ならば, u, v を始点とし,同 じホールドレジスタのみを通り同じ外部出力に至る経 路対が存在する.このことより,分岐枝  $y_i$ , $y_i$  が分離 可能である条件は, $y_i$ , $y_j$  を始点とし外部出力に至る 任意の経路対  $P_i$ ,  $P_j$  に対し,  $first(P_i) \neq first(P_j)$ または  $first\_depth(P_i) \neq first\_depth(P_i)$  と言い換 えることができる.各外部入力 x の各分岐枝  $y_i$  に対 し,集合  $D(y_i) = \{(r,d)|y_i$  を始点とする経路 P が 存在し,  $r = first(P), d = first\_depth(P)$ } を求め る. 各分岐枝からホールドレジスタ, または外部出力

に到達するまで,S の各信号線をたかだか 1 回探索する.分岐枝から各信号線までの順序深度の集合を考慮するので,計算量は, $O(n_f \cdot n \cdot n_l) = O(n^3)$  となる. (2) 分岐枝集合の最小分割を求める.分岐枝を頂点とし,分離可能でない頂点が連結となるグラフ $G_{sep}$  を生成し,その連結成分を求める(分離可能でないすべての頂点間を辺で接続する必要はない). 二つの分岐枝  $y_i$  , $y_j$  が分離可能とならないのは, $D(y_i) \cap D(y_j) \neq \emptyset$  となるときである.各外部入力に対し,共通の (r,d) を D(y) の要素としてもつ分岐枝y が連結となるよう  $G_{sep}$  に辺を加える.各 (r,d) に対し,分岐枝の個数回の探索を行えばよいので,計算量は, $O((n_h+n_o) \cdot n_l \cdot n_f) = O(n^3)$  となる.

以上より, $T_{C^*}(n)=O(n^3)$ となり,内部切換平衡構造順序回路のクラスは,組合せテスト生成複雑度でテスト生成可能となる.

#### 6. かすび

本論文では、組合せテスト生成アルゴリズムを用いてテスト生成可能な順序回路のクラスとして内部切換平衡構造を提案した.内部切換平衡構造のクラスは、これまでに提案されている内部平衡構造のクラスと切換平衡構造のクラスを真に含み、組合せテスト生成複雑度でテスト生成可能である.本論文では、これまで考慮されていなかったホールドレジスタの制御信号線とスイッチの故障に対し、検出可能であるための十分条件を示した.また、この十分条件だけでも、ホールドレジスタの制御信号線、スイッチの故障に対して検出可能なほとんどの故障が検出できることを実験的に評価した.更に、計算量に基づく組合せテスト生成複雑度でテスト生成可能であることを示した.

提案した内部切換平衡構造では、スイッチとホールドレジスタへの制御信号は直接外部から印加されると考えている.しかし、一般の順序回路を考えた場合、これらの制御信号は回路内部から印加される場合も存在する.今後の課題としては、制御信号が直接外部から印加される場合だけでなく、回路内部から印加される場合も考慮するように拡張することが挙げられる.

謝辞 多くの意見を頂いた奈良先端科学技術大学院 大学の大竹哲史助手,並びにコンピュータ設計学講座 の諸氏に感謝します.本研究は一部,奈良先端科学技 術大学院大学支援財団教育研究活動支援による.

#### 文 献

- A. Balakrishman and S.T. Chakradhar, "Sequential circuits with combinational test generation complexity," IEEE International Conference on VLSI Design, pp.111-117, Jan. 1996.

- [2] H. Fujiwara, Logic testing and design for testability, The MIT Press, 1985.

- [3] H. Fujiwara, "A new class of sequential circuits with combinational test generation complexity," IEEE Trans. Comput., vol.49, no.9, pp.895-905, Sept. 2000.

- [4] R. Gupta and M.A. Breuer, "Partial scan design of register transfer level circuits," J. Electronic Testing: Theory and Applications, vol.7, pp.25–46, 1995.

- [5] R. Gupta, R. Gupta, and M.A. Breuer, "The BAL-LAST methodology for structured partial scan design," IEEE Trans. Comput., vol.39, no.4, pp.538– 544, April 1990.

- [6] M. Inoue, E. Gizdarski, and H. Fujiwara, "Sequential circuits with combinational test generation complexity under single-fault assumption," J. Electronic Testing: Theory and Applications, vol.18, pp.53–60, 2002.

- [7] T. Inoue, D.K. Das, C. Sano, T. Mihara, and H. Fujiwara, "Test generation for acyclic sequential circuits with hold registers," Proc. Int. Conf. Computer-Aided Design, pp.550–556, Nov. 2000.

- [8] Y.C. Kim, V.D. Agrawal, and K.K. Saluja, "Combinational test generation for various classes of acyclic sequential circuits," Proc. Int. Test Conf., pp.1078–1087, Oct. 2001.

(平成15年1月8日受付)

#### 神野 元彰 (正員)

平 12 神戸大・工・電気電子卒 . 平 14 奈 良先端科学技術大学院大学情報科学研究科 博士前期課程了. 同年,三菱電機(株)入 社.テスト生成,テスト容易化設計,論理 合成に関心をもつ.

## 井上美智子 (正員)

昭 62 阪大・基礎工・情報卒、平元同大 大学院博士前期課程了、同年(株)富士通 研究所入社、平7 阪大大学院博士後期課程 了、奈良先端大・情報科学助手を経て,現 在,同助教授、分散アルゴリズム,グラフ 理論,テスト容易化設計,高位合成に関す

る研究に従事・工博・IEEE , 情報処理学会 , 人工知能学会各会員 .

## 藤原 秀雄 (正員:フェロー)

昭 44 阪大・工・電子卒.昭 49 同大大学院博士課程了.同大・工・電子助手,明治大・工・電子通信助教授,情報科学教授を経て,現在,奈良先端大・情報科学教授.昭 56 ウォータールー大客員助教授.昭 59 マッギル大客員準教授.論理設計論,フォー

ルトトレランス,設計自動化,テスト容易化設計,テスト生成,並列処理,計算複雑度に関する研究に従事.著書「Logic Testing and Design for Testability」(MIT Press) など.大川出版賞,IEEE Computer Society Outstanding Contribution Award,IEEE Computer Society Meritorious Service Award など受賞.情報処理学会会員.IEEE Computer Society Golden Core Member,IEEE Fellow.