# 組合せテスト生成複雑度でパス遅延故障テスト生成可能な順序回路 のクラス

三輪俊二郎 大竹 哲史 静藤原 秀雄 村

A New Class of Sequential Circuits with Combinational Test Generation Complexity for Path Delay Faults

Shunjiro MIWA<sup>†</sup>, Satoshi OHTAKE<sup>††</sup>, and Hideo FUJIWARA<sup>††</sup>

あらまし 本論文では、平衡構造順序回路のパス遅延故障テスト生成問題が、平衡構造順序回路を組合せ変換した組合せ回路のセグメント遅延故障テスト生成問題に帰着できる(組合せテスト生成複雑度でパス遅延故障テスト生成可能である)ことを示す、平衡構造順序回路は、組合せ変換した組合せ回路に対するテスト生成,及びもとの順序回路に対するテスト実行を、出力錐ごとに行わなければならず、テスト生成時間及びテスト実行時間が長くなる、この欠点を解消するために、組合せテスト生成複雑度でパス遅延故障テスト生成可能な新しい順序回路のクラスとして同位相平衡構造を定義する、本論文では更に、与えられた順序回路に対して、スキャン FFを取り除いた回路が平衡構造及び同位相平衡構造となるような部分スキャン設計法を提案する。

キーワード パス遅延故障,同位相平衡構造,組合せテスト生成複雑度,拡張部分スキャン設計,循環スキャン FF

#### 1. まえがき

近年の半導体集積技術の進歩に伴い、VLSIの集積度、動作速度は飛躍的に向上している。このような状況において、現在広く用いられている故障モデルである縮退故障に加えて、回路が設計仕様を満たす速度で動作することを確かめる遅延故障のテストが重要視されるようになった。遅延故障のモデルとしてトランジション故障、ゲート遅延故障、パス遅延故障などが提案されている[1]が、その中でもパス遅延故障は一般性のある故障モデルであることが知られている。しかし、回路内に存在するパスの数は回路規模が大きくなるにつれ指数的に増大するという欠点がある。実用的には回路内のすべてのパスをテストすることが不可能であるため、テストの対象となるパスの部分集合を求

組合せ回路におけるパス遅延故障のテストは2パ ターンテスト  $(t_1, t_2)$  を回路の動作スピードで印加し, 2 ベクトル目の応答を観測することにより行う. 組合 せ回路において,このようなベクトル対を求めるパス 遅延故障テスト生成(以下,テスト生成という)は比 較的容易であるのに対して、順序回路においては回路 内に存在するフリップフロップ(以下,FFと呼ぶ)に 任意の値を直接設定できないため、パス遅延故障に対 するテスト生成は非常に困難である.この問題を解決 するためにいくつかのテスト容易化設計法が提案され ている[5],[6].回路内のすべての FF を拡張スキャン FF (2 パターンテストを外部から設定可能な FF)[5] に変更する完全拡張スキャン設計法は,テスト生成の 対象回路(核回路)が組合せ回路になる.したがって, 組合せ回路用のテスト生成アルゴリズムを用いてテ スト生成することができるので,高い故障検出効率を 得ることができるが、テスト容易化に伴う面積オーバ ヘッドが大きいという欠点がある.この欠点を解消す るために,一部の FF を拡張スキャン FF に変更する 部分拡張スキャン設計 [6] が提案されており, 完全拡張

めるパス選択の手法[2]が提案されている.

<sup>†</sup> NEC エレクトロニクス第一カスタム LSI 事業部 , 川崎市 1st Custom LSI Division, NEC Electronics Corp., 1753 Shimonumabe, Nakahara-ku, Kawasaki-shi, 211-8668 Japan

<sup>&</sup>lt;sup>††</sup> 奈良先端科学技術大学院大学情報科学研究科,生駒市 Graduate School of Information Science, Nara Institute of Science and Technology, 8916-5 Takayama, Ikoma-shi, 630-0101 Japan

スキャン設計に比べて面積オーバヘッドを抑えることが可能になる.しかし,テスト容易化設計を行わない回路に対するテスト生成と同様に順序回路用のテスト生成アルゴリズムを用いる必要があり,また,拡張スキャンFF は生成されたテスト系列を連続時間で印加できない(2パターンテストごとにスキャンが必要である)ため,部分拡張スキャン設計を行った場合でもパス遅延故障に対するテストは依然として困難である.

本研究では,組合せテスト生成複雑度でパス遅延故 障テスト生成可能な順序回路を核回路にもつ部分ス キャン設計法について考察する. はじめに本論文では 核回路の回路構造が強平衡構造順序回路及び平衡構造 順序回路である場合について考える.強平衡構造順序 回路及び平衡構造順序回路のパス遅延故障のテスト生 成問題が,強平衡構造順序回路及び平衡構造順序回路 を組合せ変換した(すべての FF を信号線に置き換え た)組合せ回路のセグメント遅延故障のテスト生成問 題に帰着できることを示す.ここで,順序回路のパス 遅延故障テスト生成問題が,その順序回路を組合せ変 換した組合せ回路でのセグメント遅延故障テスト生成 問題に帰着できるとき、その順序回路を組合せテスト 生成複雑度でパス遅延故障テスト生成可能な順序回路 という. 具体的には, 強平衡構造順序回路及び平衡構 造順序回路を組合せ変換した組合せ回路のセグメント 遅延故障に対して生成した2パターンテストを, もと の順序回路のテスト系列に変換できることを示す. し かし,本手法では平衡構造順序回路の各外部出力に対 する出力錐(その外部出力に到達可能なすべての素子 からなる部分回路)ごとにテスト生成及びテスト実行 を行う(3.参照)ので,テスト生成時間及びテスト実 行時間がかかるという問題がある.また,部分スキャ ン設計において強平衡構造を核回路とする場合, FF のスキャン化率が高い. そこで本論文では, 組合せテ スト生成複雑度でパス遅延故障テスト生成可能な新し い順序回路のクラスとして同位相平衡構造順序回路を 定義する.これにより,平衡構造順序回路に比べFF のスキャン化率は増加するが,テスト生成時間及びテ スト実行時間は短くなると期待できる. 本論文では更 に,一般の順序回路に対して循環スキャン FF を用い た平衡構造及び同位相平衡構造に基づく順序回路の部 分スキャン設計法を提案する.

# 2. 諸 定 義

本論文では,順序回路のパス遅延故障のテスト生成

問題が組合せ回路のセグメント遅延故障のテスト生成問題に帰着できることを示す.はじめに,パス遅延故障及びセグメント遅延故障とそれらのテスト可能性,テスト生成問題帰着性を定義する.

[ 定義 1 ] (パス遅延故障 )[1],[3] 順序回路において, $g_i$  をゲートとし, $g_0$  が外部入力または FF, $g_n$  が外部出力または FFであるような連接するゲートの集合  $\{g_0,g_1,\cdots,g_n\}$  をパスという.このとき,パスの始点で起こった信号の変化が決められた時間内にパスの終点に到達しないような故障をパス遅延故障という.

[ 定義 2 ] (パス遅延故障テスト可能 ) 順序回路 S のパス遅延故障を f とし, $S_f$  を f によって故障した回路とする.以下の条件を満たすとき,パス遅延故障 f はテスト系列 t でテスト可能であるという.

- i) f の存在する組合せ部分回路 (入力として外部 入力及び FF をもち,出力として外部出力及び FF をもつ,連結した極大の組合せ回路 ) C の入力に対して,f の起こるパスに信号の変化を発生させるのに必要なベクトル対  $(t_1,t_2)$  が存在する.

- ii) 外部入力から C の入力にベクトル対  $(t_1,t_2)$  を正当化し f の起こるパスの終点に現れた  $t_2$  の応答を外部出力まで伝搬するための外部入力系列 t が存在する.

- iii) C に印加したベクトル  $t_2$  の応答を 1 システム クロック後に C の出力となる FF に取り込むことが できるか , または外部出力で観測可能である .

- iv) S に t を印加して得られた出力応答と  $S_f$  に t を印加して得られた出力応答が異なる .

[ 定義 3 ](セグメント遅延故障)[1],[4] 組合せ回路において,ゲートの段数が L である連接するゲートの集合  $\{g_1,g_2,\cdots,g_L\}$  をセグメントという.ここで,セグメントの始点で起こった信号の変化が決められた時間内にセグメントの終点に到達しないような故障をセグメント遅延故障という.あるセグメントに故障が発生すると,そのセグメントを含むすべてのパスに遅延が起こるものとする.

[ 定義 4 ] ( セグメント遅延故障テスト可能 ) 組合せ回路 C のセグメント遅延故障を f とし, $C_f$  を f によって故障した回路とする.このとき,C の入力ベクトル対  $(t_1,t_2)$  に対して, $t_1$ , $t_2$  を C に連続して印加したときの  $t_2$  の出力応答と, $t_1$ , $t_2$  を  $C_f$  に連続して印加したときの  $t_2$  の出力応答が異なるとき, $(t_1,t_2)$  を f の 2 パターンテストと呼び,f は  $(t_1,t_2)$  でテスト可能であるという.ただし,ベクトル  $t_2$  の C の外

部出力に現れた応答を任意の時刻で観測可能である.

テスト生成問題帰着性を次のように定義する.以下では,回路が与えられると,その回路に対する故障モデルが与えられるものとする.

[ 定義 5 ] ( テスト生成問題帰着性 ) 回路 C を変換  $\tau$  によって変換して得られた回路を  $C^\tau$  とする  $.C,C^\tau$  の それぞれの故障モデルにおけるある故障集合を  $F,F^\tau$  とする . このとき  $,C,C^\tau$  について次の三つの条件を満たすならば ,C における F のテスト生成問題は  $C^\tau$  における  $F^\tau$  のテスト生成問題に帰着できるという .

- i) F から  $F^{ au}$  への写像  $arphi_{ au}$  が存在する .

- ${

m ii})$  F の任意の故障 f に対して , f が C においてテスト可能ならば , かつそのときに限り  $\varphi_{\tau}(f)$  は  $C^{\tau}$  においてテスト可能である .

- iii)  $F^{\tau}$  のうち  $C^{\tau}$  でテスト可能な故障集合を F' とする . F' の任意の故障 f について  $,\bigcup_{t\in\mathcal{T}(f)}\{\sigma(t)\}\subseteq\bigcap_{g\in\varphi_{\tau}^{-1}(f)}\mathcal{T}(g)$  となる写像  $\sigma$  が存在する . ここで  $,\mathcal{T}(f)$  は故障 f に対応する回路において ,f をテスト可能なすべてのテスト系列の集合とする .

#### 3. 順序回路のクラス

順序回路は組合せ回路部分と,FF で構成される状態記憶部分からなる.本論文ではFF は D 型 FF のみを扱うものとする.

[ 定義 6 ]( 平衡構造 )[7] 順序回路 S に閉路が存在しないとき,S は無閉路構造であるという.無閉路構造の順序回路  $S_A$  の,任意の外部入力と任意の外部出力の対について,その入出力間に存在するどの経路の順序深度(経路上の FF 数)も等しいとき, $S_A$  は平衡構造であるという.

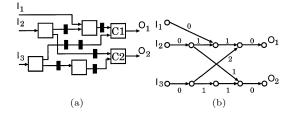

平衡構造順序回路の例を図 1(a) に示す.図中の白 と黒の四角はそれぞれ組合せ部分回路と FF を示す. [ 定義 7 ]( トポロジーグラフ ) 順序回路 S のトポ

図 1 (a) 平衡構造順序回路 S (b) S のトポロジーグラフ Fig. 1 (a) A balanced sequential circuit and (b) its topology graph.

ロジーグラフは,次のような重み付き有向グラフG = (V, A, w)である.

- *V* は *S* の外部入力,外部出力,組合せ部分回路を頂点とする集合.

- $A\subset V\times V$  は S の外部入力と組合せ部分回路の入力,組合せ部分回路の入力と組合せ部分回路の出力,組合せ部分回路の入力と外部出力を接続する信号線または FF のみを通る経路を辺とする集合 .

- $w:A \to \{0\} \cup N$  (自然数)は辺の重み( $a \in A$ に対応する S の信号線または経路上の FF の個数).

図 1(a) の平衡構造順序回路は図 1(b) に示すトポロジーグラフで表現できる.図 1(b) 中の白丸は頂点,矢印は有向辺を表し,有向辺に割り当てられた数値は,辺の重みを表す.

[ 定義 8 ] ( 強平衡構造 ) [9] 無閉路順序回路 S のトポロジーグラフ G=(V,A,w) において以下の条件を満たすような任意の整数値 t(v) を各頂点  $v\in V$  に割り当てることができるとき S は強平衡構造であるという.ここで,w(a) は辺  $a\in A$  の重みを表す.

$$t(v_i) = t(v_j) + w(a) \ \forall a(v_i \to v_j)$$

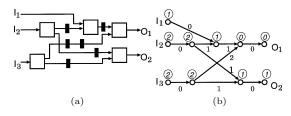

強平衡構造順序回路の例とそのトポロジーグラフを図 2 に示す.図 2 (b) のトポロジーグラフの頂点 v に割り当てられた,丸の中に示された数値は,出力  $O_1$  に対応する頂点に 0 を割り当てたときに,上式で計算された t(v) を表す.一方,図 1 の順序回路は平衡構造順序回路であるが,強平衡構造順序回路ではない. [定理 1 ] [9] 順序回路 S が平衡構造であるとき,かつそのときに限り,S の各外部出力に関する出力錐(その外部出力に到達可能なすべての素子からなる部分回路)は強平衡構造である.

[ 定義 9 ](同位相平衡構造 ) 平衡構造順序回路 S のトポロジーグラフ G=(V,A,w) において以下の条件を満たすような任意の値  $b(v)\in\{0,1\}$  を各頂点  $v\in V$

図 2 (a) 強平衡構造順序回路 S (b) S のトポロジーグラフ

Fig. 2 (a) A strongly balanced sequential circuit and (b) its topology graph.

に割り当てることができるとき S は同位相平衡構造であるという.ここで,w(a) は辺  $a \in A$  の重みを表す. $mod_2(x)$  は x を 2 で割った余りを示す.

$b(v_i) = mod_2(b(v_i) + w(a)) \quad \forall a(v_i \to v_i)$

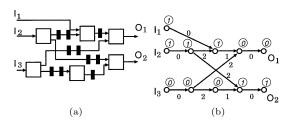

同位相平衡構造順序回路の例とそのトポロジーグラフを図 3 に示す.図 3 (b) のトポロジーグラフの頂点v に割り当てられた,丸の中に示された数値は,出力 $O_1$  に対応する頂点に 0 を割り当てたときに,上式で計算されたb(v) を表す.図 3 の回路は,強平衡構造順序回路ではない.また,図 1 は,平衡構造順序回路であるが同位相平衡構造順序回路ではない.

[ 定義 10 ] (組合せ変換) 無閉路順序回路 S のすべての FF を信号線に置き換える変換を組合せ変換と呼ぶ、以下では,無閉路順序回路 S を組合せ変換して得られた組合せ回路を C(S) と表記する.

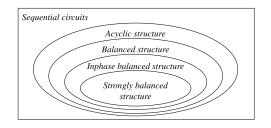

以上で挙げた無閉路順序回路,平衡構造順序回路,同位相平衡構造順序回路及び強平衡構造順序回路は以下の関係にある(図4参照).定理1とそれぞれの回路構造の定義より,{強平衡構造順序回路} ○ {同位相平衡構造順序回路} ○ {平衡構造順序回路} ○ {無閉路順序回路}が成り立つ.また,先の図1,図2,図3の回路例から,これらは真の包含関係である.強平衡構造順序回路及び平衡構造順序回路は,縮退故障に対して組合せテスト生成複雑度でテスト生成可能

図 3 (a) 同位相平衡構造順序回路 S (b) S のトポロジー グラフ

Fig. 3 (a) An inphase balanced structure and (b) its topology graph.

図 4 順序回路のクラス Fig. 4 Classes of sequential circuits.

な順序回路のクラスであることが知られている.強平 衡構造順序回路及び平衡構造順序回路 S においては, C(S) に対して縮退故障のテスト生成を行い,そこで 得られたテストベクトルをもとの順序回路 S のテスト系列に変換することができる.

平衡構造順序回路の順序深度を d とする.平衡構造順序回路は,外部入力に対してある入力パターン t を (d+1) 時刻の間保持し続ければ,外部出力でその応答を観測できるという特徴がある.

同位相平衡構造順序回路は,図 3 に示すようにすべての頂点に対して 0 または 1 の値を割り当てることが可能である.同位相平衡構造順序回路の順序深度を d とする.外部入力に対して,ある入力パターン t を各外部入力に割り当てられた値に基づくタイミングで各外部入力に (d+2) 時刻の間 1 クロックおきに与え続けると,その応答が外部出力で,各外部出力に割り当てられた値に基づくタイミングで観測できるという特徴がある.

強平衡構造順序回路は図 2 (b) に示すように,すべての頂点 v に対して整数値 t(v) を割り当てることが可能である.割り当てられる整数値の最大値を  $t_{max}$  とする.また,外部入力  $PI_i$  及び外部出力  $PO_j$  の,トポロジーグラフ G に対応する頂点をそれぞれ  $vs_i$  及び  $vd_j$  とする.強平衡構造順序回路は各外部入力に対して,ある入力パターン t の値を, $(t_{max}-t(vs_i))$  時刻に 1 回だけ与えると,その応答が各外部出力において  $(t_{max}-t(vd_j)+1)$  時刻で観測できるという特徴がある.

# 4. テスト生成問題帰着性

#### 4.1 強平衡構造

強平衡構造順序回路 S のパス遅延故障のテスト生成問題が C(S) のセグメント遅延故障のテスト生成問題に帰着できることを示す.はじめに,テスト系列の変換を定義し,次に S のパス遅延故障 f がテスト可能であるならば,C(S) の f に対応するセグメント遅延故障  $f^C$  の 2 パターンテストを変換して得られる f のテスト系列が存在することを示す.最後に S のパス遅延故障のテスト生成問題が C(S) の f に対応するセグメント遅延故障  $f^C$  のテスト生成問題に帰着できることを示す.

強平衡構造順序回路 S のトポロジーグラフを G=(V,A,w) とする . G のすべての頂点 v に整数値 t(v) を割り当てる . t(v) の最大値を  $t_{max}$  , 最小値を  $t_{min}$  と

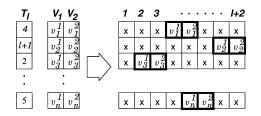

したとき, $l=t_{max}-t_{min}$ をSの伝搬深度と呼ぶ.ここで,Sの外部入力  $PI_j(j=1,2,\cdots,m)$  に対応するGの頂点を $r_j$ とする.このとき, $\alpha_j=t_{max}-t(r_j)+1$ なるベクトル  $T_I=(\alpha_1,\alpha_2,\cdots,\alpha_m)$ を,Sの印加タイミングベクトルと呼ぶ.ここで,任意のm ビットベクトル対を $V_1=(v_1^1,v_2^1,\cdots,v_m^1)$ , $V_2=(v_1^2,v_2^2,\cdots,v_m^2)$ とするとき,以下のような長さ(l+2)のm ビットベクトル系列 L を考える(図 S).i ベクトル,j ビットの値を $x_{ij}$ とする.

$$x_{ij} = \begin{cases} v_j^1 & \text{if } i = \alpha_i \\ v_j^2 & \text{if } i = \alpha_i + 1 \\ \text{don't care} & \text{otherwise} \end{cases}$$

このとき,L を (l+2) 拡張 2 パターン系列と呼ぶ. また,このようなベクトル対から拡張 2 パターン系列 への変換を (l+2) 拡張 2 パターン系列変換と呼ぶ.

また,S の外部出力  $O_i(i=1,2,\cdots,n)$  に対応する S の頂点を  $s_i$  とする.このとき, $\beta_i=t_{max}-t(s_i)+2$  なるベクトル  $T_O=(\beta_1,\beta_2,\cdots,\beta_n)$  を,S の観測タイミングベクトルと呼ぶ. $\beta_i$  は,1 時刻目から(l+2)時刻目の間に S に印加される(l+2)拡張 2 パターン系列の,2 時刻目から(l+3)時刻目までの出力応答系列(長さ(l+2))における座標を表す.ここで,(l+2)拡張 2 パターン系列を S に印加して得られる出力応答系列の  $T_O$  に示されている座標の値で構成されるベクトルを観測ベクトルと呼ぶ.

[補題 1](テスト系列の存在) 強平衡構造順序回路 S の任意のパス遅延故障 f について f がテスト可能であるならば , (l+2) 拡張 2 パターン系列である f のテスト系列が存在する .

(証明) l を S の伝搬深度とし,f が存在する組合せ部分回路を C とする.S の印加タイミングベクトルを  $T_O$  とする.パス遅延故障テスト可能性の定義 2 より,f がテスト可能であるならば,C の入力に対して,f に信号の変化を

図 5 (l+2) 拡張 2 パターン系列変換 Fig. 5 The (l+2)-extended sequence transformation.

発生させるためのベクトル対  $(t_1,t_2)$  が存在し,外部 入力から  $t_1$ ,  $t_2$  を C の入力に正当化することができ, また C に対する  $t_2$  の出力応答を外部出力へ伝搬する ことができる.ここで,fのテスト実行時間を(l+3)とする. 強平衡構造の定義 8 より C の入力に  $t_1$  を 正当化するには , C の入力に関係するすべての外部入 力に対して, $T_I$ で指定された時刻に $t_1$ を正当化する ための値を 1 回だけ印加すればよい . 同様に  $t_2$  に対 しては, $t_1$  の次の時刻でC に正当化できればよいの で, $T_I$  で指定された次の時刻で $t_2$  を正当化するため の値を外部入力に印加すればよい.ここで, $t_2$ の出力 応答を伝搬する外部出力を 〇 とする.強平衡構造の 定義 8 より,  $t_2$  の出力応答は  $T_O$  で指定された O の 時刻の次の時刻で観測でき, $t_2$ の出力応答を伝搬する ための値を外部入力へ与える時刻は  $T_I$  で指定された 時刻の次の時刻である.したがって, $t_1$ , $t_2$ の正当化 及び  $t_2$  の出力応答伝搬のための外部入力に対するテ スト系列として, (l+2) 拡張 2 パターン系列が存在 する.

[定理 2 ](出力値の一致) 強平衡構造順序回路 S について,C(S) に任意のベクトル対  $(t_1,t_2)$  を印加して得られる  $t_2$  の出力応答ベクトルを  $O^C$  とする.また,S の伝搬深度を l として, $(t_1,t_2)$  の (l+2) 拡張 2 パターン系列を S に印加して得られる観測ベクトルを  $O^S$  とする.このとき, $O^C$  と  $O^S$  は同一である.(証明) S は強平衡構造であるので, $t_2$  の値が  $T_I$  に示されたタイミングで 1 回だけ回路に印加されればその応答が  $T_O$  に示された時刻に観測できる.また C(S) に  $t_2$  を印加すると,その応答は次の時刻に観測できる.更に S と C(S) は FF を除いて同形であるので, $O_S^C = O_S^C$  である.

[ 定理 3 ] (テスト生成問題帰着性 ) 強平衡構造順序回路 S の全パス遅延故障集合 F のテスト生成問題は , C(S) に存在するセグメント遅延故障の部分集合  $F^C$  のテスト生成問題に帰着できる .

(証明)テスト生成問題帰着性の定義 5 のすべての条件を満たすことを示す.

i) 組合せ変換の定義より,S と C(S) は FF を除いて同形である. $FF_i$  は信号線  $L_i$  に置き換えられるので S 中に存在するパス( $FF_s$  から  $FF_{de}$ ,ある外部入力から  $FF_{de}$ ,からある外部出力,及び,ある外部入力からある外部出力)は C(S) に存在するセグメント( $L_s$  から  $L_{de}$ ,対応する外部入力から  $L_{de}$ , $L_s$  から対応する外部出力,及び,対応する外部入力から

対応する外部出力)と一対一に対応する.よって,S の任意のパス遅延故障 f は C(S) のあるセグメント遅延故障  $f^C$  と一対一に対応させることができる.ゆえに, $\varphi_C(f)=f^C$  なる写像  $\varphi_C$  が存在する.ここで, $F^C=\bigcup_{f\in F}\varphi_C(f)$  とする.

ii) 十分性:S の任意のパス遅延故障  $f \in F$  がテスト 可能ならば C(S) のセグメント遅延故障  $f^C = \varphi_C(f)$ がテスト可能であることを示す .  $S^f$  及び  $C(S^f)$  を ,それぞれ f 及び  $f^C$  によって故障した回路とする.こ こで l を S の伝搬深度とし ,(l+2) 拡張 2 パターン 系列変換 M の逆変換を  $M^{-1}$  とする . 補題 1 より S において f がテスト可能であるならば f f f f張 2 パターン系列  $t^S$  が存在し,  $t^S$  を S に印加した ときの出力と $S^f$ に印加したときの出力は異なる.ま た,定理2よりSに $t^S$ を印加したときに得られる 観測ベクトルと , C(S) に  $M^{-1}(t^S)$  を印加したとき の2ベクトル目の出力応答ベクトルは一致する.同様 に  $S^f$  に  $t^S$  を印加したときに得られる観測ベクトル と ,  $C(S^f)$  に  $M^{-1}(t^S)$  を印加したときの 2 ベクトル 目の出力応答ベクトルは一致する. ゆえに, $M^{-1}(t^S)$ を C(S) に印加したときの出力と  $C(S^f)$  に印加した ときの出力は異なる. したがって,Sの任意のパス遅 延故障 f が S でテスト可能ならば C(S) のセグメン ト遅延故障  $f^C = \varphi_C(f)$  がテスト可能であることが 示された.

必要性: $f^C$  が C(S) においてテスト可能であるならば, $f=\varphi_C^{-1}(f^C)$  が S においてテスト可能であることを示す. $f^C$  がテスト可能ならば, $f^C$  の 2 パターンテスト  $t^C$  が存在し, $t^C$  を C(S) に印加したときの出力は異なる.また,定理 2 より C(S) に  $t^C$  を印加したときの 2 ベクトル目の出力応答ベクトルと,S に  $M(t^C)$  を印加してときの 1 を印加したときの 1 を印加したときの 1 を印加したときの 1 を印加したときの 1 を可加したときの 1 を可加したときの 1 を可加したときの 1 を可加したときの制測ベクトルと,1 を可加したときの制測ベクトルと,1 に可加したときの出力は異なる.したがって 1 のセグメント遅延故障 1 がテスト可能ならば 1 のパス遅延故障 1 のパス遅延故障 1 がテスト可能であることが示された.

${

m iii)}$   ${

m i)}$  よりテスト対象となる故障が 1 対 1 に対応し, ${

m ii)}$  より C(S) でテスト可能なセグメント遅延故障  $f^C\in F^C$  の 2 パターンテストの集合  $T(f^C)$

に対して, $\bigcup_{t\in \mathcal{T}(f^C)}\{M(t)\}$  は S のパス遅延故障  $f=\varphi_C^{-1}(f^C)$  のテスト系列となっている.すなわち, $\bigcup_{t\in \mathcal{T}(f^C)}\{M(t)\}=\mathcal{T}(f)$  となる変換 M が存在する.以上より,定理 3 は証明された.

C(S) のある 2 パターンテスト t が , 故障  $f_1$  及び  $f_2$  を検出できるとする.定理 3 より ,  $f_1$  及び  $f_2$  に対応する S の故障  $f_1$  及び  $f_2$  は S においてテスト可能である.このとき,定理 2 より,t を (l+2) 拡張 2 パターン系列変換して得られた系列は,S において  $f_1$  及び  $f_2$  を検出できることがわかる.したがって,S が強平衡構造であるならば,C(S) のテスト生成の際に,故障シミュレーションや,パターン圧縮などの手法を用いることができ,テスト生成時間,2 パターンテスト数を削減できる.

#### 4.2 平衡構造順序回路

平衡構造順序回路 S のパス遅延故障のテスト生成問題が C(S) のセグメント遅延故障のテスト生成問題に帰着できることを示す .

[ 定理 4 ] ( テスト生成問題帰着性 ) 平衡構造順序回路 S の全パス遅延故障集合 F のテスト生成問題は , C(S) に存在するセグメント遅延故障の部分集合  $F^C$  のテスト生成問題に帰着できる .

(証明) S の任意のパス遅延故障  $f \in F$  に対して, fから到達可能な外部出力の集合を 0 とし,0 の要素 数を n とする .  $o_i \in O(i=1,2,\cdots,n)$  に関する出力 錐は,定理1より強平衡構造であるので, $o_i$ の出力 錐  $So_i$  における f のテスト生成問題は , f に対応す る  $C(So_i)$  のセグメント故障  $f^C$  のテスト生成問題に 帰着できる.したがって,f がテスト可能であるなら ば,かつそのときに限り,ある  $C(So_i)$  において  $f^C$ の 2 パターンテスト  $t_i^C$  が存在する . ここで  $So_i$  の 伝搬深度を  $l_i$  とする .  $C(So_i)$  に対して得られた 2 パ ターンテスト  $t_i^C$  は ,  $So_i$  に含まれない外部入力とは 独立に  $So_i$  の  $(l_i+2)$  拡張 2 パターン系列  $t_i^S$  に変換 できる.また, $So_i$  の外部入力に対して $So_i$  に含まれ ない外部入力とは独立に  $t_i^S$  を印加することができる. 以上より, 平衡構造順序回路 S の任意のパス遅延故障 f のテスト生成問題は C(S) のあるセグメント遅延故 障  $f^C$  のテスト生成問題に帰着できる.

C(S) のある 2 パターンテスト t が , 故障  $f_1$  及び  $f_2$  を検出できるとする . 定理 4 より ,  $f_1$  及び  $f_2$  に対応する S の故障  $f_1'$  及び  $f_2'$  は S においてテスト可能である . このとき , t を S において  $f_1'$  を検出するための系列  $t^S$  に変換することはできるが ,  $t^S$  で  $f_2'$

を検出できるとは限らない.

例:図 1 (a) の平衡構造順序回路 S について,S の組合せ部分回路 C1 及び C2 に対応する C(S) の組合せ部分回路を  $C1^C$  及び  $C2^C$  とする.C(S) のある 2 パターンテスト  $V_1=(v1_1,v1_2,v1_3)$ , $V_2=(v2_1,v2_2,v2_3)$  が,C(S) の  $C1^C$  に存在する故障  $f_1$  及び  $C2^C$  に存在する故障  $f_2$  を検出できるとする.ここで,S の, $f_1$  に対応する C1 の故障  $f_1'$  及び  $f_2$  に対応する C2 の故障  $f_2'$  のテスト系列を考える.C(S) の 2 パターンテストの値を S に印加し組合せ部分回路 C1 に  $V_1$ , $V_2$  の影響を連続で正当化するスケジューリングを考えると,入力  $I_1$ , $I_2$  及び  $I_3$  にはそれぞれ,系列( $\times v1_1v2_1\times$ ),( $v1_2v2_2\times \times$ ) 及び ( $v1_3v2_3\times \times$ ) を印加する必要がある.しかし,この印加スケジューリングでは C2 に対して,2 パターンテストの影響を正当化することができない.

したがって,S が平衡構造であるならば,C(S) ではテスト生成は出力錐ごとに行わなければならず,故障シミュレーションやパターン圧縮などの手法も,出力錐ごとにしかできないので,テスト生成時間,2 パターンテスト数が強平衡構造に比べて大きくなると考えられる.

# 4.3 同位相平衡構造

平衡構造は強平衡構造より広い回路クラスである. 強平衡構造は回路全体に対してテスト生成を行うことができるが,平衡構造はすべての出力錐ごとに個別に テスト生成を行わなければならず,テスト生成時間が 長くなる欠点がある.本論文で提案する同位相平衡構 造は,強平衡構造より広い回路クラスであり,回路全 体に対してテスト生成を行うことができる回路クラス である.

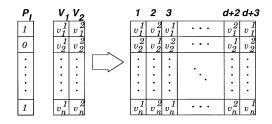

同位相平衡構造順序回路 S のトポロジーグラフを G=(V,A,w) とし,S の順序深度を d とする.G の すべての頂点 v に値  $b(v)\in\{0,1\}$  を割り当てる.ここで S の外部入力  $PI_j(j=1,2,\cdots,m)$  に対応する G の頂点を  $r_j$  とする.このとき, $\alpha_j=t(r_j)$  なるベクトルベクトル  $P_I=(\alpha_1,\alpha_2,\cdots,\alpha_m)$  を,S の印加位相ベクトルと呼ぶ.

任意の m ビットベクトル対を  $V_1=(v_1^1,v_2^1,\cdots,v_m^1)$  ,  $V_2=(v_1^2,v_1^2,\cdots,v_m^2)$  とする.ここで , 以下のような長さ (d+3) の m ビットベクトル系列 R を考える (図 6 ) .i ベクトル , j ビットの値を  $x_{ij}$  とする.

•  $\alpha_i \in P_I = 1$  のとき

図 6 (d+3) 循環系列変換

Fig. 6 The (d+3) rotating sequence transformation.

$$x_{ij} = \begin{cases} v_j^1 & \text{(} mod_2(i) = 1 \text{ のとき} \text{)} \\ v_j^2 & \text{(} mod_2(i) = 0 \text{ のとき} \text{)} \end{cases}$$

•  $\alpha_j \in P_I = 0$  のとき

$$x_{ij} = egin{cases} v_j^2 & (\ mod_2(i) = 1 \ \mathfrak{O}$$

උපි )  $v_j^1 & (\ mod_2(i) = 0 \ \mathfrak{O}$ උපි )

このとき,R を (d+3) 循環系列と呼ぶ.また,このようなベクトル対から循環系列への変換を (d+3) 循環系列変換と呼ぶ.

また,S の外部出力  $O_i(i=1,2,\cdots,n)$  に対応する G の頂点を  $s_i$  とする.このとき, $\beta_i=b(s_i)$  なるベクトル  $P_O=(\beta_1,\beta_2,\cdots,\beta_n)$  を,S の観測位相ベクトルと呼ぶ.

観測位相ベクトルの値は回路の外部出力に対応する 接点に割り当てられた値であり、故障の影響が現れる 場合、偶数時刻目に現れるか、または奇数時刻目に現 れるかを示している.

(d+3) 循環系列を S に印加して得られる出力応答系列の最後の二つのベクトルの  $T_O$  に示されている位相の値 ( 0 ならば (d+2) 番目の値 , 1 ならば (d+3) 番目の値 ) で構成されるベクトルを循環観測ベクトルと呼ぶ .

[ 定理 5 ](出力値の一致 ) 同位相平衡構造順序回路 S の順序深度を d とし,任意のベクトル対  $(t_1,t_2)$  を C(S) に印加して得られる  $t_2$  の出力応答ベクトルを  $O^C$  とする.また,ベクトル対を (d+3) 循環系列変 換して得られる (d+3) 循環系列 T を S に印加して 得られる循環観測ベクトルを  $O^S$  とする.このとき, $O^C$  と  $O^S$  は同一である.

(証明) S について,C(S) の任意のベクトル対を  $(t_1,t_2)$  とする.S の任意の出力錐  $co_i$  の順序深度を  $d_i$  とする.定理 1 より, $co_i$  は強平衡構造であり, $co_i$  の伝搬深度は順序深度  $d_i$  と等しいので, $(t_1,t_2)$  から  $co_i$  の  $(d_i+2)$  拡張 2 パターン系列  $T_i$  が得られる.

S のトポロジーグラフ G の各頂点には矛盾がないように値  $b\in\{0,1\}$  を割り当てることができるので,出力錐  $co_i$  と出力錐  $co_j$   $(i\neq j)$  が同じ外部入力  $PI_k$  をもつ場合, $PI_k$  から印加される  $T_i$  及び  $T_j$  に含まれる  $t_1$ , $t_2$  の値は,それぞれ同じ時刻に存在するか,若しくは必ず偶数時刻ずれて存在する.ゆえに,T から得られる S の (d+3) 循環系列には S のすべての出力錐の  $(d_i+2)$  拡張 2 パターン系列が埋め込まれている.よって,(d+3) 循環系列を S に印加して得られる循環観測ベクトル  $O^S$  は  $O^C$  と同一である.

同位相平衡構造順序回路 S と C(S) の間のテスト生成問題帰着性に関して,次の定理が成立する.

[ 定理 6 ]( テスト生成問題帰着性 ) 同位相平衡構造順序回路 S の全パス遅延故障集合 F のテスト生成問題は , C(S) に存在するセグメント遅延故障の部分集合  $F^C$  のテスト生成問題に帰着できる .

(証明) {同位相平衡構造順序回路} ⊂ {平衡構造順序回路}より明らか. □

C(S) のある 2 パターンテスト t が , 故障を  $f_1$  及び  $f_2$  を検出できるとする . 定理 6 より ,  $f_1$  及び  $f_2$  に対応する S の故障  $f_1'$  及び  $f_2'$  は S においてテスト可能である . このとき , 定理 5 より , t を (d+3) 循環系列変換して得られた系列は , S において  $f_1'$  及び  $f_2'$  を検出できることがわかる . したがって , S が同位相平衡構造であるならば , C(S) のテスト生成の際に , 故障シミュレーションや , パターン圧縮などの手法を用いることができ , テスト生成時間 , 2 パターンテスト数を削減できる .

#### 5. テスト容易化設計

順序回路 S 中のすべての FF の集合を Q とする Q の部分集合を  $Q_E$  として  $Q_E$  を取り除いた回路  $Q_E$  を核回路と呼ぶ  $Q_E$  の  $Q_E$   $Q_E$  の  $Q_E$   $Q_E$   $Q_E$   $Q_E$   $Q_E$   $Q_E$   $Q_E$   $Q_E$   $Q_E$   $Q_$

図 7 (a) 拡張スキャン FF (b) 循環スキャン FF Fig. 7 (a) An enhanced scan FF and (b) a rotating enhanced scan FF.

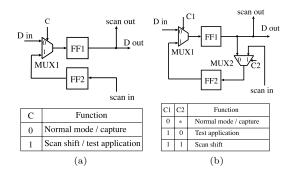

スキャン入力から設定でき,連続してそれらの値を出力できる FF を拡張スキャン FF (ESFF) と呼ぶ.

ESFF の実現例を図 7 (a) に示す . ESFF は , MUX1を 1 に制御することで 2 個の値を scan in から FF1 及び FF2 に設定することが可能 (スキャンモード) である . また , このとき 2 個の FF に設定された値を連続して D out から出力できる (テストモード). ESFFは MUX1を 0 に制御すると通常動作が可能である (通常動作モード).

[定義 12] (循環スキャン FF)[8] 任意の 2 個の値をスキャン入力から設定でき,それらの値を任意の時間保持でき,それらの値を交互に連続して出力でき,2 個の連続した入力値を実動作速度で取り込むことができる機能をもつスキャン FF を循環スキャン FF (RESFF) と呼ぶ.

RESFF の実現例を図 7(b) に示す。RESFF は,MUX1 及び MUX2 を 1 に制御することで 2 個の値を scan in から FF1 及び FF2 に設定することが可能(スキャンモード)である。また,MUX1 を 1,MUX2 を 0 に制御することで 2 個の FF に設定された値を交互に連続して D out から出力できる(テストモード)。また MUX1 を 0 に制御すると通常動作(1 個の値の取込み)が可能である(通常動作モード/取込みモード)。MUX1 及び MUX2 を 0 に制御すると連続する 2 個の値を FF に取り込むことができる(連続取込みモード)。

以下では,核回路が強平衡構造の場合,平衡構造の場合及び同位相平衡構造の場合について,ESFF 及びRESFF を用いたテスト容易化設計法とテスト実行法を述べる.

#### 5.1 核回路が強平衡構造の場合

順序回路において,核回路の回路構造が与えられたとき,最小の外部 FF の集合を求める問題をスキャン FF 選択問題という.核回路が強平衡構造の場合,この問題は NP 困難な問題であり,ネットワークフローの問題として解くヒューリスティックアルゴリズムが 提案されている [9].以下では外部 FF を ESFF 及び RESFF に変更した場合についてそれぞれのテスト実行法を示す.

順序回路 S の核回路  $S_K$  の入力数を n , 出力数を m とし ,  $S_K$  を組合せ変換した  $C(S_K)$  に対してセグメント遅延故障テスト生成して得られた 2 パターンテストを  $V_1=(v_1^1,v_2^1,\cdots,v_n^1)$  ,  $V_2=(v_1^2,v_2^2,\cdots,v_n^2)$  とする .  $S_K$  の順序深度を d , 伝搬深度を l とする .

#### 5.1.1 ESFF を用いる場合

外部 FF を ESFF に変更してテストを行う場合は , 2 個のベクトルの印加ごとにスキャンを行うため , 内部 FF にはホールド機能が必要になる .

強平衡構造である核回路  $S_K$  のパス遅延故障のテストについて考える.テスト対象となるパス f に信号の変化を発生させるためのベクトル対が f の存在する組合せ部分回路 C に正当化され,1 システムクロック後に故障の影響が f の終点となる FF に取り込まれるか外部出力で観測できる必要がある.そのため ESFF を用いて拡張 2 パターン系列を回路に印加する場合,拡張 2 パターン系列に埋め込まれている 2 パターンテスト  $(V_1,V_2)$  の, $V_2$  によって正当化される C の入力値が実動作速度で FF またはスキャン FF に取り込むか,外部出力で観測できるようなスキャン動作のスケジューリングが必要になる.

$S_K$  のトポロジーグラフ G において,すべての頂点 v には整数値 t(v) を割り当てることができる.f が存在する組合せ部分回路 C に対応する G の頂点を  $v^f$  とする.ここで,G の頂点に割り当てられる最大整数値を  $t_{max}$  とすると,C には  $(V_1,V_2)$  の影響が  $(t_{max}-t(v^f)+1)$  時刻目, $(t_{max}-t(v^f)+2)$  時刻目に現れるので,拡張 2 パターン系列の印加の際には, $(t_{max}-t(v^f)+2)$  番目のパターンを印加後,その応答を回路の通常動作の動作速度で FF に取り込むか,直接外部出力で観測する必要がある.拡張 2 パターン系列の印加スケジュールの例を図 8 に示す.上述のように,拡張 2 パターン系列の  $(t_{max}-t(v^f)+1)$  番目 及び  $(t_{max}-t(v^f)+2)$  番目のベクトルは,連続して

図 8 拡張 2 パターン系列の印加スケジュール Fig. 8 A scheduling for application of an extended two-pattern sequence.

印加できなければならないので  $(t_{max} - t(v^f) + 1)$ 番目と  $(t_{max} - t(v^f) + 2)$  番目のベクトルの間にス キャン動作が入らないように,図中のaでスキャン動 作に切り換え,これらのベクトルを拡張スキャン FF に読み込む.スキャン動作では,外部 FF はシフトレ ジスタとして動作させ,内部 FF についてはその状態 が変わらないように,ホールドしておく.次に,通常 動作に切り換えて,bで $(t_{max}-t(v^f)+2)$ 番目のべ クトルを印加した後, c で通常動作の動作速度で外部 出力で観測するか, FF または ESFF にその応答を取 り込む.通常動作モードでは,内部 FF,外部 FF と もに通常の FF として動作する.拡張2パターン系列 の  $(t_{max} - t(v^f))$  番目までの印加については,状態 を制御するだけなので, fの検出のためには特に回路 の通常動作の動作速度で印加する必要はない.また,  $(t_{max}-t(v^f)+3)$  以降の応答の伝搬についても,FF に取り込まれた応答を ESFF または外部出力へ伝搬 するだけなので, f の検出のためには特に回路の通常 動作の動作速度で印加する必要はない.したがって,  $(t_{max} - t(v^f) + 1)$  番目と  $(t_{max} - t(v^f) + 2)$  番目 以外のベクトルについては、一つずつスキャンインす るか、図のように二つずつスキャンインすればよい. ESFF に故障の影響を伝搬する場合, ESFF は一つの 値しか取り込むことができないが, 故障の影響が現れ るたかだか一つの ESFF で値を取り込めるようにス

キャンのスケジュールを決めればよい.

ここで,S の伝搬深度を l , $C(S^k)$  に対して生成される 2 パターンテストの数を j ,ESFF に変更する FF の数を p とする.一つの拡張 2 パターン系列につき最大( $\lceil (l+2)/2 \rceil+1$ )回のスキャン動作が必要であるので,1 回のテスト実行についてスキャン動作を(( $\lceil (l+2)/2 \rceil+1$ )×2p)クロック行う.一つの拡張 2 パターン系列のを用いたテスト実行時間は( $\lceil (l+2)/2 \rceil+1$ )×2p+(l+2) クロックである.

一つの拡張 2 パターン系列 T で複数の故障がテス ト可能である場合を考える .S の T によってテスト可 能な故障を  $f_1$  及び  $f_2$  とし ,  $f_1$  が存在する組合せ部 分回路を  $C_1$  ,  $f_2$  が存在する組合せ部分回路を  $C_2$  と すると, $C_1$  及び  $C_2$  に対して拡張 2 パターン系列に 埋め込まれている2パターンテストの,2ベクトル目 によって正当化される  $C_1$  及び  $C_2$  の入力値がそれぞ れの入力に対して実動作速度で正当化されなければな らない.また,それぞれの故障が発生するパスの終点 で FF に取り込まれた値を ESFF に取り込むか,また は外部出力で観測する必要がある. 故障が存在する組 合せ部分回路に割り当てられる整数値のパリティが同 じであれば,Tを用いたテスト実行は1回でよい.し かし,パリティが同じでないとき,スキャン動作のタ イミングの問題で 1 回の T の印加で  $C_1$  及び  $C_2$  に対 して,実動作速度でのテストが行えないので,この場 合は T を用いたテストを 2 回行う必要がある.この ため,一つの拡張2パターン系列Tで複数の故障が テスト可能である場合には,一つの拡張2パターン系 列について2回のテスト実行が必要になることがある.

以上より,すべての 2 パターンテストを変換した拡張 2 パターン系列を印加するのに要するテスト実行時間は, $2j((\lceil (l+2)/2 \rceil+1) \times 2p + (l+2))$  クロックとなる.

拡張 2 パターン系列には一つの 2 パターンテストの値が各入力に対して 1 回だけ配置されているので,複数の 2 パターンテストを連続して配置することでテスト実行時間の圧縮が可能である.しかし,故障による誤りが ESFF に取り込まれる時刻を故障ごとに解析する必要があり,複雑なスキャンのスケジューリングが必要になる.

テスト容易化に伴うハードウェアオーバヘッドは, 内部 FF のホールド機能のための付加回路及び,外部 FF を ESFF に変更することで一つの外部 FF につき 一つの MUX と一つの FF が必要になる.

#### **5.1.2** RESFF を用いる場合

ESFF を用いたテスト容易化設計ではスキャンの回数が多くなってしまう欠点あるが,RESFF と循環系列を用いたテストではスキャンの回数が大幅に減り,系列のスケジューリングが容易になる.また,内部FF のホールド機能が不要になる.強平衡構造順序回路は同位相平衡構造の性質をもっているので,テスト系列として (d+3) 循環系列を用いることができる.RESFF を用いて (d+3) 循環系列を核回路に印加する手続きを以下に示す.

#### [系列の印加]

$S_K$  の入力が RESFF である場合,循環系列の,それらの入力に対応するはじめの 2 個の値をスキャンインし,(d+2) 若しくは (d+3) 時刻の間,テストモードで値を印加する.外部入力である場合は,循環系列の,外部入力に対応する 2 個の値を交互に印加する.

#### [応答の観測]

$S_K$  の出力が RESFF である場合,出力応答系列の,(d+2) 番目または (d+3) 番目の値を取り込み,スキャンアウトして外部で循環観測ベクトルに対応する値を観測する.(d+2) 番目の値と(d+3) 番目の値を両方とも観測しなければならない場合には,循環系列を2度印加する必要がある.外部出力である場合は,循環観測ベクトルに対応する値を観測する.

ここで, $C(S_K)$ から生成される2パターンテスト の数を k とする . S の外部  $\operatorname{FF}$  の数を p とする . -つ の循環系列につき,スキャン動作が 4p 時刻必要であ るが,スキャンアウトと同時に次の循環系列をスキャ ンインできる.また,出力応答系列の (d+2) 番目の 値を RESFF に取り込んで観測する場合には,テスト 系列印加に (d+2) クロックを要し (d+3) 番目の値 を RESFF に取り込んで観測する場合には,テスト系 列印加に (d+3) クロックを要するので,全体のテス ト実行時間は 2k(2p+d+2)+k+2p クロックであ る. ハードウェアオーバヘッドに関しては,外部 FF を RESFF に変更した場合, ESFF を用いる場合に必 要であった,内部 FF のホールド機能が不要である. また,外部 FF を RESFF に変更するため ESFF を用 いた場合に加えて一つの RESFF につき MUX が1個 必要になる.

以上のことから, ESFF を用いるテストは RESFF を用いる場合に比べてテスト実行時間が長くなる.以下では RESFF を用いるテスト実行のみを考える.

#### 5.2 核回路が平衡構造の場合

与えられた順序回路の,核回路が平衡構造の場合のスキャン FF 選択問題を解くアルゴリズムが文献 [7] に示されており,回路トポロジーグラフにおける枝数のオーダの計算量で解くことが可能である.

平衡構造順序回路 S において C(S) で生成された 2 パターンテストは S 全体のテスト系列に変換できないので,出力錐ごとにテスト生成及びテスト実行を行う.RESFF と循環系列を用いたテストは,核回路の各出力錐ごとに 4.1 で示された方法を用いて行う.ここで,順序回路 S について,核回路  $S_K$  の任意の出力錐を  $s_i$  とする. $s_i$  の順序深度を  $d_i$  とする. $C(s_i)$  で生成された 2 パターンテストの数を  $l_i$  とする.S の外部 FF の数を p とする. $s_i$  に対するテスト実行時間は  $(2l_i(2p+d_i+2)+l_i+2p)$  クロックである.

FF をスキャン FF に変更するスキャン化率は強平 衡構造と比べて低いが,出力錐ごとにテスト生成及び テスト実行を行うため,テスト生成時間,テスト実行 時間が大きくなる.

## 5.3 核回路が同位相平衡構造の場合

任意に与えられた核回路が同位相平衡構造になるようなスキャン FF 選択問題を,以下の三つのステップに分けて解く方法を考える.

- 1) 無閉路構造抽出:核回路が無閉路構造になるように面積オーバヘッド最小の外部 FF を選択する.

- 2) 平衡構造抽出: 1) で得られた無閉路構造を核回路として,核回路が平衡構造になるような面積オーバヘッド最小の外部 FF を選択する.

- 3) 同位相平衡構造抽出: 2)で得られた平衡構造 を核回路として,核回路が同位相平衡構造になるよう な面積オーバヘッド最小の外部 FF を選択する.

スキャン FF 選択問題の 1) 及び 2) はそれぞれ文献 [7] 及び [9] に示されている.3) は 2) で求められた平衡構造順序回路 S のトポロジーグラフ G から辺集合  $A_I$  を除去することによりグラフが同位相平衡構造となる辺集合  $\sum_{a\in A_I} w(a)$  が最小となるものを求める.すなわち,グラフにおいてできるだけ多くの頂点に対して  $b(v_i)=mod_2(b(v_j)+w(a))$  を満たす任意の値を割り当てることができればよい.ここではすべての辺 a に対して値  $x(a)\in\{0,1\}$  を割り当て,条件式を  $b(v_i)=mod_2(b(v_j)+w(a)+x(a))$  に変更することで,3) の手続きは以下に示す整数計画問題として

定式化できる.

最小化: x(a)=1 である辺の数 条件:  $\forall v_i$ ,  $v_i \in V$ ,  $\forall a(v_i \rightarrow v_i)$

$b(v_i) = mod_2(b(v_j) + w(a) + x(a))$

b(v) ,  $x(a) = \{0, 1\}$

RESFF と循環系列を用いたテストは 4.1 で示された方法を用いる。同位相平衡構造である核回路を  $S_K$  とし, $C(S_K)$  から生成される 2 パターンテストの数を l とする。外部 FF の数を p とする。一つの循環系列につき,テストパターンの設定,応答の観測のためのスキャン動作には 4p クロックかかり,また,出力応答系列の (d+2) 番目の値を RESFF に取り込んで観測する場合には,テスト系列印加に (d+2) クロックを要し,(d+3) 番目の値を RESFF に取り込んで観測する場合には,テスト系列印加に (d+3) クロックを要するので,全体のテスト実行時間は 2l(2p+d+2)+k+2p クロックである.

スキャン化率は核回路が強平衡構造である場合より も低いが,平衡構造の場合より高くなる.しかし,回 路全体でテスト生成及びテスト実行が可能であるので, テスト生成時間及びテスト実行時間は平衡構造の場合 より小さくなる.

# 6. む す び

本論文では,はじめに強平衡構造順序回路及び平衡 構造順序回路のパス遅延故障テスト生成問題が, もと の順序回路を組合せ変換した組合せ回路のセグメント 遅延故障テスト生成問題に帰着できることを示した. 平衡構造順序回路の場合,出力錐ごとにテスト生成及 びテスト実行を行うので,テスト生成時間及びテスト 実行時間が長いという問題があった.また,強平衡構 造順序回路でテスト容易化設計を行う場合, FF のス キャン化率が高いという問題があった. そこで本論文 では,組合せテスト生成複雑度でパス遅延故障テスト 生成可能な新しい順序回路のクラスとして同位相平衡 構造順序回路を提案した.また,一般の順序回路に対 して強平衡構造,平衡構造,及び同位相平衡構造に基 づく, 循環スキャン FF を用いた部分スキャン設計法 を提案した、また、それぞれの場合について、テスト 実行時間を理論的に評価した.

謝辞 本研究に関し,多くの意見を頂いた大阪大学の増澤利光教授,及び,奈良先端科学技術大学院大学の井上美智子助教授をはじめコンピュータ設計学講座の諸氏に感謝致します.本研究は一部,日本学術振

興会・科学研究費補助金・基盤研究 B(2)課題番号 09480054)の研究助成,奈良先端科学技術大学院大学 支援財団教育研究活動支援,及び日本学術振興会・科学研究費補助金・奨励研究(A)課題番号 12780226)による.

#### 対 対

- A. Krstic and K.T.(Tim) Cheng, Delay fault testing for VLSI circuits, Kluwer Academic Publishers, 1998.

- [2] K. Heragu, V.D.Agrawal, and M.L. Bushnell, "Statistical methods for delay fault coverage analysis," Proc. VLSI Design '95, pp.166-170, 1995.

- [3] G.L. Smith, "Model for delay faults based upon paths," Proc. ITC '85, pp.342-349, 1985.

- [4] K. Heragu, J.H. Patel, and V.D. Agrawal, "Segment delay faults: A new fault model," Proc. VTS '96, pp.32–39, 1996.

- [5] B.I. Dervisoglu and G.E. Strong, "Design for testability: Using scanpath techniques for path-delay test and mesurement," Proc. ITC '91, pp.365-374, 1991.

- [6] T.J. Chakraborty, V.D. Agrawal, and M.L. Bushnell, "Design for testability for path delay faults in sequential circuits," Proc. DAC '93, pp.453–457, 1993.

- [7] R. Gupta, P. Gupta, and M.A. Breuner, "The BAL-LAST methodology for structured partial scan design," IEEE Trans. Comput., vol.39, no.4, pp.538– 544, April 1990.

- [8] H. Kim and J.P. Hayes, "Delay fault testing of designs with embeded IP cores," Proc. VTS '99, pp.160-167, 1999.

- [9] A. Balakrishnan and S.T. Chakradhar, "Sequential circuits with combainational test generation complexity," Proc. VLSI Design '96, pp.111-117, 1996.(平成 14 年 12 月 13 日受付, 15 年 4 月 6 日再受付)

#### 三輪俊二郎

平 11 岡山大・工・情報工卒 . 平 13 奈良 先端大・情報科学・博士前期課程了 . 現在 , NEC エレクトロニクス (株)勤務 . LSI 設計開発に従事 .

## 大竹 哲史 (正員)

平 7 電通大・電通・情報工卒. 平 9 奈良 先端大・情報科学・博士前期課程了. 平 11 同大博士後期課程了. 現在, 奈良先端大・ 情報科学研究科助手. 平 10 日本学術振興 会特別研究員. VLSI CAD, テスト容易化 設計, テスト生成アルゴリズムに関する研

究に従事 . 平 13 年度本会情報システムソサイエティ論文賞受賞 . IEEE Computer Society 会員 .

#### 藤原 秀雄 (正員:フェロー)

昭 44 阪大・工・電子卒.昭 49 同大大学院博士課程了.同大・工・電子助手,明治大・工・電子通信助教授,情報科学教授を経て,現在,奈良先端大・情報科学教授.昭 56 ウォータールー大客員助教授.昭 59 マッギル大客員準教授.論理設計論,フォー

ルトトレランス,設計自動化,テスト容易化設計,テスト生成,並列処理,計算複雑度に関する研究に従事.著書「Logic Testing and Design for Testability」(MIT Press) など.大川出版賞,IEEE Computer Society Outstanding Contribution Award,IEEE Computer Society Meritorious Service Award など受賞.情報処理学会会員,IEEE Computer Society Golden Core Member,IEEE Fellow.