# PAPER Acceleration of Test Generation for Sequential Circuits Using Knowledge Obtained from Synthesis for Testability

Masato NAKAZATO<sup>†a)</sup>, Satoshi OHTAKE<sup>†</sup>, Members, Kewal K. SALUJA<sup>††</sup>, Nonmember, and Hideo FUJIWARA<sup>†</sup>, Fellow

**SUMMARY** In this paper, we propose a method of accelerating test generation for sequential circuits by using the knowledge about the availability of state justification sequences, the bound on the length of state distinguishing sequences, differentiation between valid and invalid states, and the existence of a reset state. We also propose a method of synthesis for testability (SfT) which takes the features of our test generation method into consideration to synthesize sequential circuits from given FSM descriptions. The SfT method guarantees that the test generator will be able to find a state distinguishing sequence. The proposed method extracts the state justification sequence from the FSM produced by the synthesizer to improve the performance of its test generation process. Experimental results show that the proposed method can achieve 100% fault efficiency in relatively short test generation time.

key words: sequential circuit, test generation, synthesis for testability, finite state machine, test knowledge

## 1. Introduction

For general sequential circuits, it is difficult to achieve 100% fault efficiency in reasonable test generation time even for single stuck-at faults. The full-scan design is utilized to ease the test generation for sequential circuits [1]. However, we cannot perform *at-speed testing* for full-scan designed sequential circuits. To realize at-speed testing, an efficient test generation algorithm for sequential circuits, which generates tests for all the detectable faults and identifies all the untestable faults in reasonable test generation time, is necessary.

Most test generation algorithms for sequential circuits (e.g. HITEC [2], VERITAS [3], STALLION [5] and FASTEST [6]) employ a time frame expansion model of a sequential circuit. The time frame expansion model is a combinational circuit that simulates the exact behavior of the sequential circuit for a given number of time frames.

The HITEC is a well known test generator for sequential circuits. This method consists of two phases. The first phase is the forward time processing phase in which a fault is activated and the resulting fault effect is propagated to a primary output. The second phase is the backward time processing phase which justifies the state required for activating the fault.

a) E-mail: masato-n@is.naist.jp

DOI: 10.1093/ietisy/e90-d.1.296

The VERITAS test generation method is an extension of the finite state machine (FSM) verification approach. This method constructs a product machine of a good FSM and its faulty version, and carries out reachability analysis by traversing the product machine. The information obtained by the reachability analysis is used to generate a test sequence. Although this simplifies generation of state justification sequences, it is not efficient to generate tests because it has to deal with huge product machines.

In this paper, we propose a method of accelerating test generation for sequential circuits using the knowledge about a set of state justification sequences, the bound on the maximum length of state distinguishing sequences, the information about the valid states and the value of the reset state. We assume that circuits are given in FSM description. For circuits designed at register transfer level (RTL), controllers of the circuits are generally specified by FSM description. The proposed method is effective for such controllers. The sequential circuit is synthesized from a given FSM by a synthesis for testability (SfT) method proposed in this paper which takes the features of our test generation method into consideration. The SfT method guarantees the existence of state distinguishing sequences of the specified length by making the given FSM reduced. Thus, the performance of the test generator is improved as it uses state justification sequences extracted from the completely specified state transition function of the FSM produced by the synthesizer. The proposed method can completely identify every fault in the circuit obtained by the proposed SfT method to be detectable or untestable. In our experiments, 100% fault efficiency is achieved for all the benchmark circuits in relatively short test generation time.

The rest of this paper is organized as follows. Section 2 introduces our circuit model and defines the basic concepts. Section 3 gives the outline of the proposed method. Section 4 describes the proposed SfT algorithm. Section 5 describes the proposed test generation algorithm for sequential circuits synthesized by our SfT method. Section 6 reports the results of experiments of our method using MCNC benchmark circuits. Finally, Sect. 7 describes conclusions and future work.

## 2. Preliminaries

In this paper we consider synchronous sequential circuits composed of combinational logic and D-type flip-flops

Manuscript received May 8, 2006.

Manuscript revised July 3, 2006.

<sup>&</sup>lt;sup>†</sup>The authors are with the Nara Institute of Science and Technology (NAIST), Kansai Science City, 630–0192 Japan.

<sup>&</sup>lt;sup>††</sup>The author is with the University of Wisconsin-Madison, USA.

(FFs). All the FFs are controlled by a single clock. We assume that a reset state is defined and a reset signal is available. We also assume that both the good and the faulty circuits can be put on the reset state by applying the reset signal. We consider the single stuck-at fault model but the faults on the clock lines, inside the FFs, and on the reset lines are not included in the fault set.

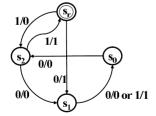

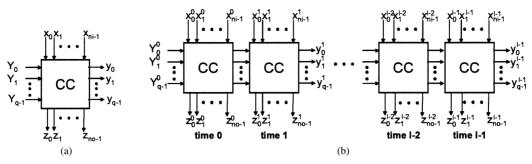

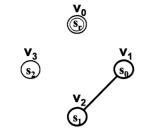

This paper deals with completely and incompletely specified Mealy-type FSMs. A Mealy-type FSM M is defined as a 6-tuple  $\langle \Sigma, O, S, s_r, \delta, \lambda \rangle$ .  $\Sigma = \{x_0 x_1 \dots x_{n_i-1} \mid$  $x_k \in \{0, 1, X\}, 0 \leq k < n_i\}$  is the set of *input vectors* and  $O = \{z_0 z_1 \dots z_{n_o-1} \mid z_k \in \{0, 1, X\}, 0 \le k < n_o\}$  is the set of *output vectors*, where X is the don't care, and  $n_i$ and  $n_o$  are the numbers of inputs and outputs, respectively.  $S = \{s_r, s_0, s_1, \dots, s_{n-2}\}$  is the set of states, where n is the number of states and  $s_r$  is the reset state. The functions  $\delta$  and  $\lambda$  are the state transition function  $S \times \Sigma \to S$  and the output function  $S \times \Sigma \to O$ , respectively. We assume that all the states defined in the FSM are reachable from the reset state  $s_r$ . For example, an incompletely specified Mealy-type FSM is shown in Fig. 1. A sequential circuit  $M_s$  composed of a combinational circuit part (CC) and FFs as shown in Fig. 2 is synthesized from an FSM, where  $x_0, x_1, x_2, \ldots, x_{n_i-1}$  are the primary inputs,  $z_0, z_1, z_2, \ldots, z_{n_o-1}$  are the primary outputs and r is the reset input. We classify states represented by FFs of  $M_s$  into valid states and invalid states as defined below.

**Definition 1** (Valid State and Invalid State): A state  $s_i$  represented by the FFs of a sequential circuit  $M_s$  is valid if  $s_i$  is reachable from the reset state of  $M_s$ . Otherwise,  $s_i$  is invalid.

**Definition 2** (State Distinguishing Sequence): Let *I* be an input sequence of an FSM *M*. Let  $o_i$  and  $o_j$  be output sequences of *I* for *M* with states  $s_i$  and  $s_j$ , respectively. *I* is called a state distinguishing sequence with respect to the pair of states  $s_i$  and  $s_j$  if  $o_i$  and  $o_j$  are not identical.

Fig. 1 An incompletely specified finite state machine.

**Fig. 2** A sequential circuit  $M_s$  synthesized from an FSM.

**Definition 3** (Reduced FSM): An FSM is said to be reduced if every pair of states has at least one state distinguishing sequence.

The proposed test generation method employs a time frame expansion model for the test generation.

**Definition 4** (Time Frame): A time frame is the combinational circuit extracted from a sequential circuit by treating its present state lines and next state lines as pseudo primary inputs and pseudo primary outputs, respectively.

**Definition 5** (Time Frame Expansion Model): A time frame expansion model of length l ( $l \ge 2$ ) for a sequential circuit is a combinational circuit constructed by connecting time frames such that the pseudo primary outputs of a time frame i ( $0 \le i \le l - 2$ ) is connected to the pseudo primary inputs of a time frame i + 1.

Examples of a time frame and a time frame expansion model are shown in Fig. 3 (a) and (b), where  $(Y_0^i, Y_1^i, \ldots, Y_{q-1}^i)$  and  $(y_0^i, y_1^i, \ldots, y_{q-1}^i)$  are the pseudo primary inputs and the pseudo primary outputs of each time frame *i*, respectively.

## 3. Outline of the Proposed Method

The proposed method consists of an SfT method and a test generation method for sequential circuits synthesized by the SfT method. The SfT method synthesizes a sequential circuit to have the three specific characteristics from a given FSM. The proposed test generation method for the sequential circuit utilizes higher level knowledge of its characteristics. By considering each characteristic, we can accelerate the fault excitation, the state justification and the error propagation, respectively. These three specific characteristics are the following.

- **Characteristic I:** Any state in a sequential circuit synthesized from an FSM can be identified as either valid or invalid.

- **Characteristic II:** There exists one to one correspondence between each state of the FSM and each valid state of the sequential circuit.

- **Characteristic III:** For each pair of states in the sequential circuit, there exists a state distinguishing sequence. The maximum length of distinguishing sequences is *k* which is known.

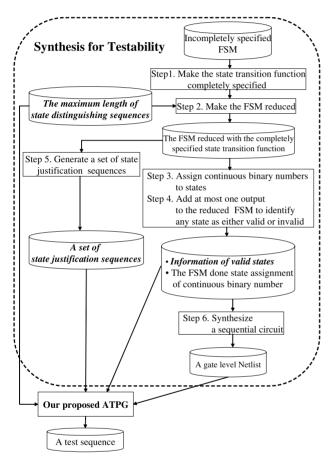

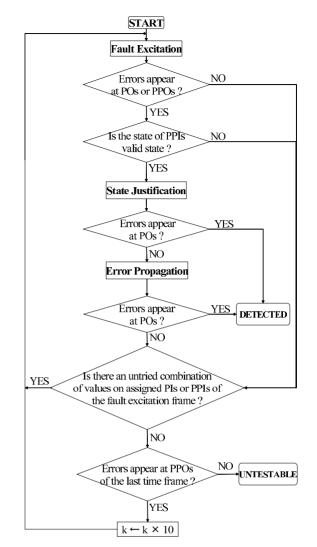

The flow chart of the proposed method is shown in Fig. 4. The area surrounded by the dotted line shows the SfT method and the outside area is our proposed automatic test pattern generation (ATPG) method. The italicized types in Fig. 4 show knowledge extracted by the SfT. The knowledge is useful for the proposed test generation as follows.

# Information of valid states:

In a justification process of test generation, we don't need to justify a fault excitation state of a sequential circuit from the reset state if the fault excitation state is invalid. We can

Fig. 3 A time frame of a sequential circuit  $M_s$  (a) and a time frame expansion model of  $M_s$  (b).

Fig. 4 The flow chart of the proposed method.

prune the search space of the justification process if we utilize the knowledge that helps to identify the fault excitation state as either valid or invalid. The knowledge "information of valid states" can be obtained since Characteristic I is satisfied. We can accelerate the whole fault excitation process during executing our proposed ATPG by reducing the number of calls of the fault excitation procedure by utilizing this information.

## A set of state justification sequences:

The state transition function of a given FSM is incompletely specified. The behavior of the FSM and the behavior of a sequential circuit synthesized from the FSM may be different, because the state transition function of the FSM is appropriately specified during the synthesis process and the state transition function of the sequential circuit becomes completely specified. We can justify the state of the sequential circuit easily if we can utilize the knowledge that helps to justify it by utilizing an input sequence, which is extracted from the FSM description, from the reset state to the excitation state. The knowledge "a set of state justification sequences" can be obtained since Characteristic II is satisfied. We can accelerate the state justification process using this information.

## The maximum length of state distinguishing sequences:

In general, we can't know the number of time frames which are required for propagating errors from the fault excitation frame to primary outputs of a sequential circuit in advance. However, we may limit the number of time frames expanded from the fault excitation frame if we have the knowledge of the number. The knowledge "the maximum length of state distinguishing sequences" is given by k since Characteristic III is satisfied. We can accelerate the error propagation process using this information.

## 4. Synthesis for Testability

In this section, we describe the proposed synthesis for testability (SfT) method for FSMs in detail. In the method, a sequential circuit which has three specific characteristics described in Chapter 3 is synthesized from a given FSM. In order to synthesize a sequential circuit with such characteristics, a given FSM is modified as follows.

- Appropriate values are assigned to some of the coordinates which have don't care values in output vectors of the FSM.

- Extra outputs, if needed, are added to the FSM and appropriate values are assigned to them.

## 4.1 Formulation of SfT Problem

We formulate the SfT problem as an optimization problem as follows.

- **Input:** An FSM with a reset state and the maximum length of state distinguishing sequences.

- **Output:** A gate level netlist of a sequential circuit which has the three characteristics with a reset, a set of state justification sequences and the number of valid states.

Objective: Minimization of the number of extra outputs.

#### 4.2 Synthesis for Testability Algorithm

In this section, we propose a heuristic algorithm of the SfT since the minimization of the number of extra outputs is NP hard. The heuristic algorithm of the SfT consists of 6 steps as follows:

- **Step 1:** Make the state transition function completely specified

- Step 2: Make the FSM reduced

- **Step 2.1:** Try to generate state distinguishing sequences of length 1 for each pair of states of the FSM

- **Step 2.2:** Generate the *k*-partial state distinguishing tree in order to confirm that there exists a state distinguishing sequence of length less than or equal to *k* for each pair of states of the FSM and a state compatibility graph

- **Step 2.3:** Determine the number of extra outputs from the state compatibility graph

- **Step 3:** Assign continuous binary numbers to states in order to identify as either a valid or an invalid state

- **Step 4:** Add an extra output to the FSM in order to guarantee existence of a state distinguishing sequence of length 1 for each pair of any valid state and any invalid state

- Step 5: Generate a set of state justification sequences

- **Step 6:** Synthesize a sequential circuit

In the heuristic algorithm, we use a *k*-partial state distinguishing tree and a state compatibility graph. We first define them as follows.

To clarify the discussion of state distinguishing sequences, we extend the definition of the successor tree defined in the literature [4] as follows.

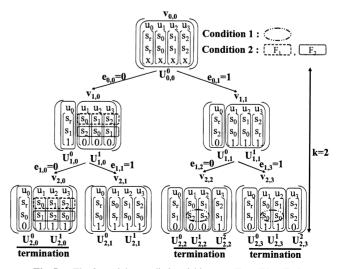

**Definition 6** (*k*-Partial State Distinguishing Tree): Let *M* be an FSM. Let  $T_k = (V_{T_k}, E_{T_k})$  be a tree of level  $k \ (0 \le k)$ , where  $V_{T_k}$  is a set of nodes  $\{v_{i,j_i} \mid 0 \le i \le k, 0 \le j_i < |\Sigma|^i\}$  and  $E_{T_k}$  is a set of edges  $\{(v_{i,j_i}, v_{i+1,j_i:|\Sigma|+t}) \mid 0 \le i < k, 0 \le j_i < k\}$  $|\Sigma|^i, 0 \le t < |\Sigma|$ . An edge  $(v_{i,j_i}, v_{i+1,j_i:|\Sigma|+t})$  is also referred to as  $e_{i,j_t:|\Sigma|+t}$  and  $\sigma_t \in \Sigma$  is associated with the edge. Let  $\mathcal{U}$  be a set of states, which will be tried to be distinguished, of M and it is referred to as an *initial uncertainty*. Let  $U_{i,i}^p$ be a set of 3-tuples  $\{u_n \mid 0 \le n < |\mathcal{U}|\}$  and be associated with  $v_{i,i}$ , where p is the characteristic number and a 3-tuple  $u_n \in U_{i,j_i}^p$  is composed of  $s_n \in \mathcal{U}$ ,  $s_\ell$  which is a state succeeded by applying the input sequence, which corresponds to a path from  $v_{0,0}$  to  $v_{i,i}$ , to  $s_n$ , and  $o_\ell$ , which appears as the last output vector by applying the input sequence to  $s_n$ , and is denoted in  $\langle s_n, s_\ell, o_\ell \rangle$ . Here,  $u_n$  is called a *distinguished* state history (DSH). For each  $U_{i,j_i}^p$  of  $v_{i,j_i}$ , sets of DSHs of  $v_{i+1,j_i:|\Sigma|+t}$  are generated so that the DSHs are obtained by applying  $\sigma_t$  to M with the state of the second element of each  $u_n \in U_{i,j_i}^p$  and these are classified into the sets where a set has the DSHs whose third elements are the same and they are different from the third elements of the DSHs in the other sets. The tree  $T_k$  is called a *k*-partial state distinguishing tree.

Figure 5 shows the 2-partial state distinguishing tree  $T_2 = (V_{T_2}, E_{T_2})$  for the FSM of Fig. 1. Here, we suppose an initial uncertainty  $\mathcal{U}$  of the FSM is a set of all the states of the FSM. Suppose a set of DSHs,  $U_{0,0}^0 = [u_0, u_1, u_2, u_3] = [\langle s_r, s_r, X \rangle, \langle s_0, s_0, X \rangle, \langle s_1, s_1, X \rangle, \langle s_2, s_2, X \rangle]$  is assigned to  $v_{0,0} \in V_{T_2}$ , where X is don't care vector such that all the bits of the output vector are don't care. By applying the vector  $\sigma_1 = 1$  to each DSH of  $v_{0,0}$ , two sets  $U_{1,1}^0$  and  $U_{1,1}^1$ , where  $U_{1,1}^0$  is  $[u_0] = [\langle s_r, s_2, 0 \rangle]$  and  $U_{1,1}^1$  is  $[u_1, u_2, u_3] = [\langle s_0, s_0, 1 \rangle, \langle s_1, s_0, 1 \rangle, \langle s_2, s_r, 1 \rangle]$ , respectively, are associated with  $v_{1,1}$ . By applying the sequence  $\sigma_1 \sigma_0 = 10$  to each DSH of  $v_{0,0}$ , three sets  $U_{2,2}^0$ ,  $U_{2,2}^1$  and  $U_{2,2}^2$ , where  $U_{2,2}^0$  is  $[u_0] = [\langle s_r, s_1, 0 \rangle], U_{2,2}^1$  is  $[u_1, u_2] = [\langle s_0, s_2, 0 \rangle, \langle s_1, s_2, 0 \rangle]$  and  $U_{2,2}^2$  is  $[u_3] = [\langle s_2, s_1, 1 \rangle]$ , respectively, are associated with  $v_{2,2}$ .

**Definition 7** (State Compatibility Graph): An undirected graph  $G = (V_G, E_G)$ , where  $v \in V_G$  is a vertex corresponding to a state of an FSM and  $e \in E_G$  is an edge corresponding to a pair of indistinguishable states of the FSM, is said to be *a state compatibility graph*.

$\mathcal{U}$  is the initial uncertainty of an FSM. Let  $D_s^{j_k}$  be a set of the distinguished states for  $s \in \mathcal{U}$  of a leaf node  $v_{k,j_k} \in$  $V_{T_k}$  of a k-partial state distinguishing tree  $T_k$  obtained from the FSM where a distinguished state is a state in  $\mathcal{U}$  except for s and is distinguishable from s. For all the leaf node of  $T_k$ , a set of states, which are distinguished from s, of  $\mathcal{U}$  is obtained by the following formula:  $\bigcup_{j_k=0}^{|\Sigma|^k} D_s^{j_k}$ . The set of indistinguishable states of s is the complement of  $\bigcup_{j_k=0}^{|\Sigma|^k} D_s^{j_k}$ for  $\mathcal{U}$ . We make the state compatibility graph based on pairs of indistinguishable states obtained from the above. Figure 6 shows the state compatibility graph corresponding to Fig. 5.

**Fig. 5** The 2-partial state distinguishing tree  $T_2 = (V_{T_2}, E_{T_2})$ .

Fig. 6 The state compatibility graph corresponding to Fig. 5.

In this figure, indistinguishable states are  $s_0$  and  $s_1$ .

Then, we describe the process for every step in detail. **Step 1:** Let  $s_i$  be a state in M such that, there exist input vectors for which next states of the state are not specified in the state transition function. For each input vector  $\sigma \in \Sigma$ , which is not defined for a transition from the state  $s_i$ , of M, a state transition from  $s_i$  to  $s_i$  (i.e., a self-loop) in M for  $\sigma$ is added to the state transition function. An output vector  $o_i$  for the self-loop is added to the output function. All the bits of  $o_i$  are don't care. The FSM obtained in this step is referred to as  $M^{\alpha}$ .

**Step 2:** To make every pair of states defined in  $M^{\alpha}$  distinguishable, we perform the following three processes.

**Step 2.1:** For each input vector  $\sigma \in \Sigma$  of M, we try to distinguish all the pairs of states  $s_i$  and  $s_j$  ( $s_i \neq s_j$ ) of M. We perform the following two processes.

**Step 2.1.1:** Let  $o_i$  and  $o_j$  be output vectors of  $\sigma$  for  $M^{\alpha}$  with  $s_i$  and  $s_j$ , respectively. We assign '0' or '1' to appropriate don't care bits of  $o_i$  in order to differentiate  $o_i$  and  $o_j$  if  $o_j$  is covered by  $o_i$ . Here, we define the relation between vectors a and b which have don't care values. We say that a covers b if  $A \supset B$ , where A and B are the sets of values represented by a and b, respectively.

**Step 2.1.2:** If  $o_i$  and  $o_j$  are the same and still have don't care bits, we assign '0' or '1' to some don't care bits of  $o_i$  and  $o_j$  to make  $o_i$  and  $o_j$  different. Let K be a set of such the same output vectors. Let  $X (= x_0x_1 \dots x_{n_X-1})$  be a vector composed of don't care bits in  $\kappa \in K$ , where  $n_X$  is the number of don't care bits in  $\kappa$ . The number of values represented by X is  $2^{n_X}$ . If  $|K| \le 2^{n_X}$ , the unique value can be assigned to each  $\kappa$ . In this case, for each  $\kappa$ , we assign an unique value to each  $\kappa$  so that the number of the same output vectors is minimized. In this case, the continuous binary number is cyclically assigned to the don't care bits in each  $\kappa$ . The FSM obtained in this step is referred to as  $M^{\beta}$ .

**Step 2.2:** We construct the *k*-partial state distinguishing tree to examine whether a pair of states  $s_i$  and  $s_j$  of M could be distinguishable by applying input sequences of length less than or equal to *k* to  $M^\beta$  with  $s_i$  and with  $s_j$ . We use the following two conditions of pruning for construction of the tree. Here, *v* and  $U^p$  are a current observed node of the *k*-partial state distinguishing tree and a set of DSHs of *v* whose the third elements are the same and they are different from the third elements of DSHs in the other sets. Let  $V_q$  be a set of nodes existing on the path from the root to *v*. Let

$U_q^p$  be a set of DSHs of  $v_q \in V_q$  whose the third elements are the same and they are different from the third elements of DSHs in the other sets. Let  $F_1(U^p)$  and  $F_2(U^p)$  be a set of first elements of all the DSHs in  $U^p$  and a set of the second elements of all the DSHs in  $U^p$ , respectively.

**Condition 1:** For each  $U^p$  of v such that  $|U^p| \ge 2$ , all the elements of  $F_2(U^p)$  are the same.

**Condition 2:** There exists  $v_q$  such that for each  $U^p$ , whose number of DSHs is larger than 1, of v, there exists  $U_q^p$ , which satisfies  $F_1(U_q^p) = F_1(U^p)$  and  $F_2(U_q^p) = F_2(U^p)$ , of  $v_q$ .

If v satisfies Condition 1 or Condition 2, v is a termination node. For example, in Fig. 5,  $v_{2,2}$  and  $v_{2,3}$  satisfy Condition 1 and  $v_{2,0}$  satisfies Condition 2. For  $v_{2,2}$ , all the elements of  $F_2(U_{2,2}^1)$  are the same state  $s_2$ . For  $v_{2,0}$ ,  $F_1(U_{2,0}^1)$ and  $F_2(U_{2,0}^1)$  of  $v_{2,0}$  are equal to  $F_1(U_{1,0}^1)$  and  $F_2(U_{1,0}^1)$  of  $v_{1,0}$  on the path from  $v_{0,0}$  to  $v_{2,0}$ , respectively. In this case, the level of termination nodes is the same as the maximum level of the 2-partial state distinguishing tree.

**Step 2.3:** We construct the state compatibility graph obtained from the *k*-partial state distinguishing tree for representing all the indistinguishable state pairs of  $M^{\beta}$ .

For example, we obtain the state compatibility graph in Fig. 6 from Fig. 5. We can see that the indistinguishable states are  $s_0$  and  $s_1$  in the state compatibility graph.

We perform the following process in order to distinguish these indistinguishable states. Some outputs are added to  $M^{\beta}$  to distinguish all the indistinguishable state pairs. The problem to find the minimum number of additional outputs to distinguish all the indistinguishable state pairs is solved as a vertex coloring problem [7] of the state compatibility graph. The number of outputs to be added to  $M^{\beta}$  is obtained by the following formula:  $n_a = \left\lceil \frac{\log_2 C}{|\Sigma|} \right\rceil$ , where *C* is the number of colors obtained by solving the vertex coloring problem and  $n_a$  is the number of the additional outputs.

Let *P* be a set of values represented by the additional outputs. Let  $f_i$  be a mapping  $\Sigma \stackrel{f_i}{\longmapsto} P$  such that  $f_i \neq f_j$ ,  $\forall i, j \mid 1 \leq i, j \leq C \land i \neq j$ . For any  $\sigma \in \Sigma$ , the output function of  $M^\beta$  is changed so that the value of the additional outputs become  $f_i(\sigma)$  for the state corresponding to each vertex, whose degree is more than or equal to 1, of the state compatibility graph. Thus, a state distinguishing sequence of length less than or equal to *k* is guaranteed for any state pair. The FSM obtained by this step is referred to as  $M^\gamma$ .

**Step 3:** Let  $n_s$  be the number of states of the FSM  $M^{\gamma}$ . The number of FF,  $n_{ff}$ , in a sequential circuit synthesized from  $M^{\gamma}$  is equal to  $\lceil \log_2 n_s \rceil$ . The number of valid states of the circuit is equal to  $n_s$  and the number of invalid states,  $n_{iv}$ , is equal to  $2^{n_{ff}} - n_s$ . Binary numbers within the range of 0 to  $n_s - 1$  are used for the state assignment of  $M^{\gamma}$  and binary numbers within the range of the state variables of invalid states of the sequential circuit. The value assigned to the reset state  $s_r$  is referred to as  $n_r$ .

**Step 4:** To guarantee existence of a state distinguishing sequence of length 1 for each pair of any valid state and any invalid state of the sequential circuit synthesized by the SfT,

one output is added to the FSM if  $n_{iv}$  is not equal to 0. This process means that a pair of any valid state and any invalid state is made distinguishable in order to realize Characteristic III. For a transition from a valid state to a valid state, '0' is assigned to the output. For a transition from an invalid state, '1' is assigned to the output. For a transition from a valid state to an invalid state, we have already considered in Step 1; all the transitions from valid states are succeeded by valid states. The FSM obtained by this step is referred to as  $M^{\epsilon}$ .

**Step 5:** For each valid state of  $M^{\epsilon}$ , an input sequence to reach the state from the reset state is generated by a breadth-first search on the state transition graph of  $M^{\epsilon}$ . By searching breadth-first fashion, the shortest input sequence is guaranteed for each state. The input sequence is called a state justification sequence.

A set of state justification sequences for all the valid states of  $M^{\epsilon}$  is referred to as  $S_{si}$ .

**Step 6:** A gate level sequential circuit is synthesized from  $M^{\epsilon}$  by a logic synthesis tool.

#### 5. Test Generation Algorithm for Sequential Circuits

In this section, we describe the proposed test generation method that utilizes the knowledge of  $S_{si}$ : a set of state justification sequences, k: the maximum length of state distinguish sequences,  $n_s$ : the number of valid states, and  $n_r$ : the value of a reset state extracted by the SfT.

Our test generation method uses a time frame expansion model. A time frame expansion model has multiple faults because every time frame has the same single stuck-at fault. Therefore, our test generation method uses a 9 valued logic system [8], [9] for the test generation to deal with multiple faults.

Figure 7 shows the flow chart of our test generation method for sequential circuits. The proposed test generation method consists of three processes: fault excitation, state justification and error propagation.

#### 5.1 Fault Excitation

For a target fault, fault excitation finds an excitation vector which is assigned to primary inputs and pseudo primary input to produce errors and to propagate them to the primary outputs and/or the pseudo primary outputs of the fault excitation frame. The pseudo primary input part of an excitation vector is referred to as an excitation state  $n_e$ . The number of valid states,  $n_s$ , helps generating a valid excitation vector which is an excitation vector whose excitation state is a valid state. If an excitation state is valid, the state may be justified from the reset state. However, if the excitation state is invalid, state justification is not required because the state cannot be justified from the reset state. Hence, the proposed method can prune a part of search space of a test generation. This search space pruning is realized by comparing  $n_s$  with  $n_e$ . If  $n_e$  is less than  $n_s$ , the excitation state is valid. Otherwise, the state is invalid. This feature saves a large amount

**Fig.7** The flow chart of the proposed test generation method for sequential circuits.

of time for trying to generate invalid excitation vector and trying to justify the invalid excitation state. If there exists no valid state to excite the fault, the fault is proved untestable.

#### 5.2 State Justification

Once an excitation vector is found, state justification is performed. The excitation state must be justified for both the fault-free circuit and the faulty circuit. We have a set of state justification sequences,  $S_{si}$ , for the fault-free circuit. The fault-free state justification can be easily done by choosing the state justification sequence for the excitation state from  $S_{si}$ . No backtracking is required and no failure can occur in this step. The next step is to confirm if the fault-free state justification sequence is also valid for the faulty circuit. This is confirmed by fault simulation using the fault-free state justification sequence and observing if any invalidation occurs. An invalidation means that a state transition of the faulty circuit is different from the fault free circuit. If an invalidation occurs, the state justification sequence cannot justify the given excitation state because the state justification sequence is not guaranteed to work under the faulty circuit. However, if an invalidation occurs, some error must appear on the pseudo primary outputs of some frame (we call this an actual excitation state) between the reset frame and the fault excitation frame. We try to propagate errors from the actual excitation state. If some error appears on the primary outputs between the reset frame and the fault excitation frame, the fault is detected.

## 5.3 Error Propagation

If a fault is not identified as detected or untestable by the first two processes, error propagation is performed. Time frames of length k are added to the (actual) fault excitation frame. The error propagation process determines primary input values of the expanded time frames to propagate an error to a primary output. This process may not propagate any error to any primary output and any pseudo primary output because errors may be masked by the multiple faults within the added k time frames. In this case, we try to search a different excitation state by returning to the fault excitation process. On the other hand, any error is not propagated to any primary output but any error is propagated to some pseudo primary output of the last time frame. This is because k-state distinguishing sequence is not guaranteed for faulty circuit. Therefore, in order to make error propagation complete, the number of time frames expanded from the fault excitation frame has to be increased (e.g.,  $k = k \times 10$ , where this number 10 might be changed empirically). We perform fault excitation again.

#### 6. Experimental Results

Table 1 shows characteristics of the MCNC FSM benchmarks [10] and the results of SfT. All the experiments except for the proposed SfT were performed on a SUN Blade 2000 (CPU 1 GHz  $\times$  2) with 8 GB memory. The experiments for the proposed SfT were performed on a PC/AT machine (CPU Athlon 3000+) with 1 GB memory. Design Compiler (Synopsys) is used as a logic synthesis tool for the Step 6 of the proposed SfT method. The number of benchmarks is 53. For all the benchmarks, the proposed method could perform until Step 5. However, Design Compiler was unable to perform Step 6 for 14 benchmarks because of restrictions on Design Compiler. One of the restrictions is that the size of FSM descriptions which Design Compiler can read is limited.

All the benchmarks shown in Table 1 were synthesized by using some optimization options which optimize the area and the delay of a circuit. The first four columns give the benchmark name and the numbers of primary inputs, primary outputs and states, respectively. The column "k" gives the maximum length of the state distinguishing sequences. The columns "#EO," "HOH" and "#MLG" give the results of the proposed SfT. The column "#EO" denotes the number of extra outputs added to each benchmark. The column

| bbsse         9         7         13         2         1         43.03         28         33           bbtas         4         2         65         1         3.45         11         5           beecount         5         4         7         2         1         12.82         27         1           cse         9         7         16         0         27.3         22         30           dk14         5         5         7         1         1         -0.28         22         20           dk15         5         5         4         1         0         0         18         18           dk16         4         3         27         1         -1.28         12         13           dk17         4         3         8         0         0         15         11           dk27         3         2         7         2         1         -1.28         12         14           dk27         3         2         7         2         1         35.15         18         22           ex1         11         19         20         1         14.6 |          |        |         | 115101 |   |     | nai ks anu | 4N            |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|---------|--------|---|-----|------------|---------------|-------------|

| bbara         6         2         10         3         2         3.36         14         17           bbsse         9         7         13         1         43.03         28         33           bbtas         4         2         65         1         3.45         11         33           beccount         5         4         7         2         1         12.82         27         1           cse         9         7         16         0         27.3         22         33           dk14         5         5         7         1         1         -0.28         22         20           dk15         5         5         4         0         0         18         13           dk17         4         3         8         0         0         15         15           dk27         3         2         72         1         -1.28         12         33           ex1         11         19         201         1         69.61         34         33           ex3         4         2         92         1         39.56         17         14     | Circuit  | #Input | #Output | #State | k | #EO | HOH (%)    | #IVI<br>Prop. | LG<br>Orig. |

| bbtas         4         2         65         1 $3.45$ 11 $3.45$ beecount         5         4         72         1         12.82         27         1           cse         9         7         161         0         27.3         22         30           dk14         5         5         7         1         1 $-0.28$ 22         20           dk15         5         5         4         1         0         0         18         13           dk16         4         3         27         2         1 $-1.28$ 12         33           dk17         4         3         81         0         0         15         11           dk27         3         2         72         1 $-1.28$ 12         33           ex1         11         19         201         1         69.61         34         33           ex4         8         9         141         1         16.36         16         23           ex4         8         9         141         1         16.36         16         24                                                                        |          |        |         |        |   |     |            |               | 17          |

| bbtas         4         2         65         1 $3.45$ 11 $3.45$ beecount         5         4         72         1         12.82         27         1           cse         9         7         161         0         27.3         22         30           dk14         5         5         7         1         1 $-0.28$ 22         20           dk15         5         5         4         1         0         0         18         13           dk16         4         3         27         1 $-1.28$ 12         33           dk17         4         3         81         0         0         15         11           dk27         3         2         72         1 $-1.28$ 12         33           ex1         11         19         201         1         69.61         34         33           ex3         4         2         102         1         35.15         18         22           ex4         8         9         141         1         16.36         16         2                                                                                   | bbsse    | 9      | 7       | 13     | 2 | 1   | 43.03      | 28            | 34          |

| beecount       5       4       7       2       1       12.82       27       1         cse       9       7       161       0       27.3       22       30         dk14       5       5       71       1 $-0.28$ 22       20         dk15       5       41       0       0       18       13         dk16       4       3       27       1 $9.76$ 48       39         dk17       4       3       81       0       0       15       11         dk27       3       2       72       1 $-1.28$ 12       34         ex1       11       19       201       1       69.61       34       33         ex3       4       2       102       1       35.15       18       22         ex4       8       9       141       1       16.36       16       22         ex4       8       9       141       1       16.36       16       22         ex5       4       2       92       1       39.56       17       13         ex6       7 <td< td=""><td>bbtas</td><td>4</td><td>2</td><td>6</td><td>5</td><td>1</td><td>3.45</td><td>11</td><td>8</td></td<>                         | bbtas    | 4      | 2       | 6      | 5 | 1   | 3.45       | 11            | 8           |

| dk14       5       5       71       1 $-0.28$ 22       22         dk15       5       5       41       0       0       18       13         dk16       4       3       272       1       9.76       48       33         dk17       4       3       81       0       0       15       11         dk27       3       2       72       1 $-1.28$ 12       33         ex1       11       19       201       1       69.61       34       33         ex3       4       2       102       1       35.15       18       22         ex4       8       9       14       1       16.36       16       23         ex5       4       2       92       1       39.56       17       13         ex6       7       8       81       0 $-1.69$ 17       24         keyb       9       2       191       1       44.6       36       29         kirkman       14       6       161       0       104.34       45       44         lion9       4                                                                                                                                       | beecount | 5      | 4       | 7      |   | 1   |            | 27            | 11          |

| dk15       5       4       1       0       0       18       13         dk16       4       3       27       1       9.76       48       39         dk17       4       3       8       1       0       0       15       11         dk27       3       2       7       2       1       -1.28       12       33         ex1       11       19       201       1       69.61       34       33         ex3       4       2       102       1       35.15       18       22         ex4       8       9       14       1       16.36       16       22         ex5       4       2       92       1       39.56       17       13         ex6       7       8       8       0       -1.69       17       20         keyb       9       2       19       1       144.6       36       21         ilion       4       1       42       0       0       9       17       33         mc       5       5       4       1       0       0       6       33       33                                                                                                            | cse      | 9      | 7       | 16     | 1 | 0   | 27.3       | 22            | 30          |

| dk 16       4       3 $272$ 1 $9.76$ 48 $39$ dk 17       4       3       81       0       0       15       11         dk 27       3       2 $72$ 1 $-1.28$ 12       3         ex1       11       19       201       1 $69.61$ 34       3         ex3       4       2       102       1 $35.15$ 18       2         ex4       8       9       141       1 $16.36$ 16       2         ex5       4       2       92       1 $39.56$ 17       13         ex6       7       8       81       0 $-1.69$ 17       20         keyb       9       2       191       1       44.6       36       21         kirkman       14       6       161       0       104.34       45       44         lion       4       1       42       0       0       9       12         lion9       4       1       96       1       14.29       17       33         mc <td< td=""><td>dk14</td><td>5</td><td>5</td><td>7</td><td>1</td><td>1</td><td>-0.28</td><td>22</td><td>26</td></td<>                                                                                                     | dk14     | 5      | 5       | 7      | 1 | 1   | -0.28      | 22            | 26          |

| dk17       4       3       81       0       0       15       11         dk27       3       2       72       1       -1.28       12       3         ex1       11       19       201       1       69.61       34       3         ex3       4       2       102       1       35.15       18       2         ex4       8       9       141       1       16.36       16       2         ex5       4       2       92       1       39.56       17       13         ex6       7       8       81       0       -1.69       17       20         keyb       9       2       191       1       44.6       36       29         kirkman       14       6       161       0       104.34       45       44         lion       4       1       42       0       0       9       17       33         mc       5       5       41       0       0       6       33       33       33       34       33         planet       9       19       48.2       1       24.76       41                                                                                                 | dk15     | 5      | 5       | 4      | 1 | 0   | 0          | 18            | 18          |

| dk27       3       2       7       2       1 $-1.28$ 12       3         ex1       11       19       201       1       69.61       34       33         ex3       4       2       102       1       35.15       18       22         ex4       8       9       141       1       16.36       16       23         ex5       4       2       92       1       39.56       17       14         ex6       7       8       81       0 $-1.69$ 17       20         keyb       9       2       191       1       44.6       36       24         kirkman       14       6       161       0       104.34       45       44         lion       4       1       42       0       0       9       17       33         mc       5       5       41       0       0       6       33       33       34       33       34       33         planet       9       19       48.2       1       24.76       41       33       33.04       100       56       56       514.8                                                                                                             | dk16     | 4      | 3       | 27     | 2 | 1   | 9.76       | 48            | 39          |

| ex1       11       19       201       1       69.61       34       33         ex3       4       2       102       1       35.15       18       22         ex4       8       9       141       1       16.36       16       23         ex5       4       2       92       1       39.56       17       18         ex6       7       8       81       0       -1.69       17       20         keyb       9       2       191       1       44.6       36       29         kirkman       14       6       161       0       104.34       45       44         lion       4       1       42       0       0       9       17       33         mc       5       5       41       0       0       6       35         opus       7       6       101       1       28.52       21       24.76         planet1       9       19       48.2       1       24.76       41       33         pma       10       6       201       1       -5.83       47       6         s1488                                                                                                 | dk17     | 4      | 3       | 8      | 1 | 0   | 0          | 15            | 15          |

| ex34210135.151822ex489141116.361623ex54292139.561718ex678810-1.691720keyb92191144.63629kirkman1461610104.344544lion414200917lion94196114.291733mc554100633opus76101128.522122planet91948.2124.764133pma1082411303.0410059s11062011-5.83476s1488101948.21-0.714888s1494101948.21-0.714888s1494101948.21-1.47294s20813218.322.412324s27616224.41413s2869713.21-1.47294sxe9716.1077.27 </td <td>dk27</td> <td>3</td> <td>2</td> <td>7</td> <td>2</td> <td>1</td> <td>-1.28</td> <td>12</td> <td>5</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | dk27     | 3      | 2       | 7      | 2 | 1   | -1.28      | 12            | 5           |

| ex4       8       9       141       1       16.36       16       2:         ex5       4       2       92       1       39.56       17       13         ex6       7       8       81       0       -1.69       17       20         keyb       9       2       191       1       44.6       36       29         kirkman       14       6       161       0       104.34       45       44         lion       4       1       42       0       0       9       17       33         mc       5       5       41       0       0       6       33       33         planet       9       19       48.2       1       24.76       41       33         pma       10       8       24.1       1       303.04       100       59         s1       10       6       20.1       1       -5.83       47       6         s1488       10       19       48.2       1       -0.71       48       88         s1494       10       19       48.2       2       -4.1       1       1                                                                                                  | ex1      | 11     | 19      | 20     | 1 | 1   | 69.61      | 34            | 35          |

| ex4       8       9       141       1       16.36       16       2:         ex5       4       2       92       1       39.56       17       13         ex6       7       8       81       0       -1.69       17       20         keyb       9       2       191       1       44.6       36       29         kirkman       14       6       161       0       104.34       45       44         lion       4       1       42       0       0       9       17       33         mc       5       5       41       0       0       6       33       33         planet       9       19       48.2       1       24.76       41       33         pma       10       8       24.1       1       303.04       100       59         s1       10       6       20.1       1       -5.83       47       6         s1488       10       19       48.2       1       -0.71       48       88         s1494       10       19       48.2       2       -4.1       1       1                                                                                                  | ex3      | 4      | 2       | 10     | 2 | 1   | 35.15      | 18            | 23          |

| ex54292139.561718ex678810 $-1.69$ 1720keyb92191144.63629kirkman1461610104.344544lion414200917lion94196114.291733mc554100633opus76101128.522122planet91948.2124.764133pma10824.11303.0410059s110620.11 $-5.83$ 4766s1488101948.21 $-0.71$ 4888s1494101948.21 $-20.73$ 4277s20813218.322.412324s27616224.41411s2985621.86211.68107144s386971321 $-1.47$ 29styr1110301262.424133styr1110301262.424133styr1110301262.424134styr11<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ex4      | 8      | 9       | 14     | 1 | 1   |            | 16            | 25          |

| ex678810 $-1.69$ 1720keyb92191144.63629kirkman1461610104.344544lion414200912lion94196114.291733mc554100635opus76101128.522124planet919482124.764133planet1919482124.764133pma1082411303.0410059s11062011-5.83476s148810194821-0.714848s149410194821-0.714844s20813218322.412324s27616224.41413s286971321-1.472944s420212181256.021424styr1110301262.424133sse97161077.277644tma962011120.75533tbk8 <t< td=""><td>ex5</td><td>4</td><td>2</td><td>9</td><td>2</td><td>1</td><td></td><td>17</td><td>18</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ex5      | 4      | 2       | 9      | 2 | 1   |            | 17            | 18          |

| keyb92191144.63629kirkman1461610104.344544lion414200917lion94196114.291733mc554100636opus76101128.522123planet919482124.764133planet1919482124.764133pma1082411303.0410059s11062011-5.83476s148810194821-0.714888s149410194821-20.734273s20813218322.412324s27616224.41413s286971321-1.47294s420212181256.021424styr1110301262.424133sse97161077.277644tma962011120.75533tbk83321136.39466tav64 <td< td=""><td>ex6</td><td>7</td><td>8</td><td>8</td><td>1</td><td>0</td><td>-1.69</td><td>17</td><td>20</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ex6      | 7      | 8       | 8      | 1 | 0   | -1.69      | 17            | 20          |

| lion414200917lion94196114.291733mc554100633opus76101128.522124planet91948.2124.764133planet191948.2124.764133pma10824.11303.0410059s110620.11-5.834766s1488101948.21-0.714888s1494101948.21-0.734277s20813218.322.412324s27616224.41411s29856218.6211.68107144s3869713.21-1.47294s42021218.1256.021424styr111030.1262.424130sse9716.1077.277644tma9620.11120.7555tbk8332.1136.394666tav6443004850tav64<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |        | 2       | 19     | 1 | 1   | 44.6       | 36            | 29          |

| lion94196114.291733mc554100633opus76101128.522122planet919482124.764133planet1919482124.764133pma1082411303.0410055s11062011-5.83476s148810194821-0.714888s149410194821-0.734277s20813218322.412324s27616224.41411s29856218.6211.68107144s386971321-1.47294s42021218.1256.021424s42021218.1256.021424s42021218.1077.277644s42021218.1077.277644thma9620.11120.75536thk8332.1136.394666thk8332.1136.394666thk8 <td>kirkman</td> <td>14</td> <td>6</td> <td>16</td> <td>1</td> <td>0</td> <td>104.34</td> <td>45</td> <td>44</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | kirkman  | 14     | 6       | 16     | 1 | 0   | 104.34     | 45            | 44          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |        | 1       | 4      | 2 | 0   |            | 9             | 12          |

| opus761011 $28.52$ 2122planet9194821 $24.76$ 4133planet19194821 $24.76$ 4133pma1082411 $303.04$ 10059s11062011 $-5.83$ 476s148810194821 $-0.71$ 48s149410194821 $-0.71$ 48s2081321822.4123s27616224.41411s298562186211.68107s420212181256.021424s420212181262.424130sse9716077.277644tma962011120.75533tbk8332136.394666tav6443004850train114111228.832614                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | lion9    | 4      | 1       | 9      | 6 | 1   | 14.29      | 17            | 33          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | mc       | 5      | 5       | 4      | 1 | 0   | 0          | 6             | 5           |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | opus     | 7      | 6       | 10     | 1 | 1   | 28.52      | 21            | - 28        |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | planet   | 9      | 19      | 48     | 2 | 1   | 24.76      | 41            | 33          |

| s1       10       6       201       1 $-5.83$ 47       6'         s1488       10       19       482       1 $-0.71$ 48       88         s1494       10       19       482       1 $-20.73$ 42       7'         s208       13       2       183       2       2.41       23       2'         s27       6       1       62       2       4.4       14       11'         s298       5       6       2186       2       11.68       107       14'         s386       9       7       132       1 $-1.47$ 29       4'         s420       21       2       181       2       56.02       14       2'         styr       11       10       301       2       62.42       41       30'         sse       9       7       161       0       77.27       76       4'         tma       9       6       201       1       120.75       5       3'         ttk       8       3       321       1       36.39       46       6'         ttk <td>planet1</td> <td>9</td> <td>19</td> <td>48</td> <td>2</td> <td>1</td> <td>24.76</td> <td>41</td> <td>33</td>                    | planet1  | 9      | 19      | 48     | 2 | 1   | 24.76      | 41            | 33          |

| s148810194821 $-0.71$ 4888 $s1494$ 10194821 $-20.73$ 4277 $s208$ 13218322.412324 $s27$ 616224.41413 $s298$ 562186211.68107144 $s386$ 971321 $-1.47$ 294 $s420$ 212181256.021424 $styr$ 1110301262.424130 $sse$ 97161077.277644tma962011120.75536tbk83321136.394666tav6443004850train1141112228.832614                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | pma      | 10     | 8       | 24     | 1 | 1   | 303.04     | 100           | - 59        |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | s1       | 10     | 6       | 20     | 1 | 1   | -5.83      | 47            | 6           |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | s1488    | 10     | 19      | 48     | 2 | 1   | -0.71      | 48            | - 88        |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | s1494    | 10     | 19      | 48     | 2 | 1   | -20.73     | 42            | 73          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | s208     | 13     | 2       | 18     | 3 | 2   | 2.41       | 23            | 24          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | s27      | 6      | 1       | 6      | 2 | 2   | 4.4        | 14            | 1.          |

| s420       21       2       18       1       2       56.02       14       22         styr       11       10       30       1       2       62.42       41       30         sse       9       7       16       0       77.27       76       44         tma       9       6       20       1       1       120.75       5       30         tbk       8       3       32       1       1       36.39       46       66         tav       6       4       43       0       0       48       50         train11       4       1       11       2       28.83       26       19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | s298     | 5      | 6       | 218    | 6 | 2   | 11.68      | 107           | 140         |

| styr         11         10         30         1         2         62.42         41         30           sse         9         7         16         0         77.27         76         44           tma         9         6         20         1         1         120.75         5         5           tbk         8         3         32         1         1         36.39         46         6           tav         6         4         43         0         0         48         50           train11         4         1         11         2         28.83         26         19                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | s386     | 9      | 7       | 13     | 2 | 1   | -1.47      | 29            | 4           |

| sse         9         7         161         0         77.27         76         44           tma         9         6         201         1         120.75         5         3           tbk         8         3         321         1         36.39         46         6           tav         6         4         43         0         0         48         50           train11         4         1         112         2         28.83         26         19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | s420     | 21     | 2       | 18     | 1 |     | 56.02      | 14            | 24          |

| tma         9         6         201         1         120.75         5         3           tbk         8         3         321         1         36.39         46         6           tav         6         4         43         0         0         48         56           train11         4         1         112         2         28.83         26         19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | styr     |        | 10      | 30     | 1 | 2   |            |               | 30          |

| tbk         8         3         321         1         36.39         46         6           tav         6         4         43         0         0         48         50           train11         4         1         112         2         28.83         26         19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | sse      | 9      | 7       | 16     | 1 | 0   | 77.27      | 76            | 48          |

| tav         6         4         43         0         0         48         50           train11         4         1         112         2         28.83         26         19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tma      | 9      | 6       | 20     | 1 | 1   | 120.75     | 5             | 8           |

| train11 4 1 112 2 28.83 26 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tbk      | 8      | 3       | 32     | 1 | 1   | 36.39      | 46            | 6           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 6      | 4       | 4      | 3 | 0   | 0          | 48            | 50          |