# 連続可検査性に基づくコアベースシステムオンチップの テスト容易化設計法

米田 友和<sup>†</sup> 藤原 秀雄†

A DFT Method for Core-Based Systems-on-a-Chip Based on Consecutive Testability

Tomokazu YONEDA<sup>†</sup> and Hideo FUJIWARA<sup>†</sup>

あらまし コアベースシステムオンチップ(SoC)が可検査であるためには、それを構成するコア自身が可検 査(高品質のテスト系列が提供される)であり、かつ SoC の外部から内部の各コアへのテストアクセスが可能で ある必要がある. 更に, このテストアクセス方式によりコア間の信号線も可検査である必要がある. SoC では縮 退故障などのような論理故障のみならず、遅延故障などのようなタイミング故障のテストも重要となる、そのた めには、コアに実動作速度(at-speed)で任意のテストパターンを連続して印加でき、その応答を連続して観測 できる必要がある、本論文では、このようなテストアクセスを可能とする性質として、コアに対して連続透明性、 SoC に対して連続可検査性なる新しい概念を提案し,連続可検査な SoC を実現するためのテスト容易化設計法

キーワード テスト容易化設計,コアベースシステムオンチップ,テストアクセス機構,連続透明性,連続可 検査性

### 1. まえがき

近年,半導体技術の進歩により,シリコンチップ上 に搭載することのできるトランジスタ数は増加の一途 をたどっている.これにより従来は複数のLSIで構成 していたシステムを,各LSIをコアと呼ばれる機能ブ ロックとして再利用し、システム全体を一つの LSI で 実現するコアベースシステムオンチップ (core-based Systems-on-a-Chip,以下SoC)が注目されている. 複数の LSI の機能を 1 チップに集積した場合,ボード へ搭載するチップ数の低減による実装面積の縮小化, 実装コストの低減,更に高速化といった効果をもつ. また,設計済みの IP (Intellectual Property)コアを 利用することで短期間で大規模な回路の設計が可能と なる.しかし現在,この SoC のテスト技術の開発が課 題[1]となっている.

SoC では,各コアに対してテスト系列が供給され,

コアの入出力が直接制御/観測可能であれば,この供 給されるテスト系列でそのコアをテストすることが可 能である.このため SoC のテストは,テスト系列を SoC 外部からコアへ印加しその応答を SoC 外部で観 測(テストアクセス)することで行われる.したがっ て SoC が可検査であるためには,コア自身が可検査 (高品質なテスト系列が提供される)であり,かつコ アへのテストアクセスが可能である必要がある.更に, コア間の信号線も可検査である必要がある.

テストアクセス方式には,テストバス方式[2],[3], 境界スキャン方式 [4], [5], 透明経路方式 [6]~[8] など がある.テストバス方式はSoCの外部入力から外部出 カヘテストデータを伝搬するためのバスを付加し,更 に各コアの入力にマルチプレクサを付加し通常動作時 の入力とテスト実行時の入力を切り換えることでテス トアクセスを実現する方式である.この方式はテスト 実行時間は短いが,面積/遅延オーバヘッドが大きい という欠点がある.更にコア間のテストが困難である という問題点がある.

境界スキャン方式は,SoC内のすべてのコアの入 出力にスキャンフリップフロップを挿入し、スキャン

Science and Technology, 8916-5 Takayama-cho, Ikoma-shi, 630-0101 Japan

<sup>&</sup>lt;sup>†</sup> 奈良先端科学技術大学院大学情報科学研究科,生駒市 Graduate School of Information of Science, Nara Institute of

パスを形成する.このスキャンパスを利用し,各コアの入出力値を SoC 外部から直接制御/観測可能とすることでテストアクセスを実現する方式である.この方式はコア間のテストはできるが,テスト実行時間は長く,更に面積/遅延オーバヘッドが大きいという欠点がある.

透明経路方式は,テストバス方式や境界スキャン方式とは異なり,コア内部の回路要素や信号線を利用してコアの内部に透明経路と呼ばれるテストデータを伝搬するための経路を実現している.これにより SoCの既存の接続線を利用したテストアクセスを実現している.この方式はコア間のテストができ,更に境界スキャン方式よりも低い面積/遅延オーバヘッド,短いテスト実行時間を達成している.

SoCでは縮退故障などのような論理故障のみならず,遅延故障などのようなタイミング故障のテストも重要となる.したがって,SoCのコアに対してはタイミング故障を対象としたテスト系列が供給される場合も想定される.このように,コアには様々な故障モデルを対象とした様々なテスト系列が供給され,そのコアがSoCに組み込まれた後でも,その系列を用いて想定した故障を完全にテストすることが必要となる.そのためには,各コアへ任意のテスト系列を実動作速度で連続してSoCの外部から印加し,その応答をSoCの外部で観測(連続テストアクセス)できる必要がある.テストバス方式はこの連続テストアクセスはできるが,コア間のテストが困難である.一方,境界スキャン方式と透明経路方式はコア間のテストはできるが,連続テストアクセスができない.

本論文ではこのような連続テストアクセスを可能とし、かつコア間のテストを可能とする性質として、コアに対して連続透明性、SoCに対して連続可検査性なる新しい概念を提案し、連続可検査な SoC を実現するためのテスト容易化設計法を示す、連続可検査な SoCは、すべてのコアとすべての信号線に対して連続テストアクセスが可能であり、任意のテスト系列を実動作速度で連続してコアや信号線に印加し、観測することができるので、コア単体に対してテスト可能な故障は、SoCに組み込まれた後でもテスト可能であることを保証する。

以下, 2. では本論文で対象とする SoC のモデル化を行い, 3. では SoC の連続可検査性について述べる. 4. で SoC を連続可検査にするためのテスト容易化設計法について述べ, 5. でまとめを行う.

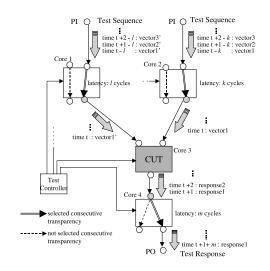

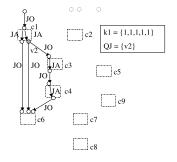

図 1 コアベースシステムオンチップ Fig. 1 Core-based systems-on-a-chip.

# 2. コアベースシステムオンチップ (SoC)

本章では、本論文で対象とする SoC について述べる. SoC は信号線と回路要素で構成される(図1). 回路要素は SoC の外部入力、外部出力、コアに分類され、信号線を接続する端子をもつ. コアは一般に複数の入力端子と出力端子をもち、各端子のビット幅は必ずしも同じでない. 外部入力は出力端子のみからなる回路要素、外部出力は入力端子のみからなる回路要素とみなす. 信号線は回路要素の出力端子と入力端子を接続する. 出力端子には複数の信号線が接続できるが(ファンアウト可能)、入力端子に接続できる信号線は一つとする.

## 3. 連続可検査性に基づく SoC のテスト

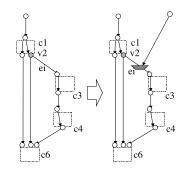

本章では,連続可検査性に基づくSoCのテストにつ いて述べる、連続可検査な SoC とその連続テストア クセスを図2に示す.コアの入力端子の連続透明性と は,その入力端子に入力される任意の長さの系列を値 を変えることなく,出力側に連続したクロックサイク ルで伝搬できる性質をいう. 図2のコア4において, 灰色の入力端子は連続透明であり,時刻t+1からの 連続した時刻で入力されるコア3のテスト応答系列を m サイクル後の時刻 t+1+m から連続して出力可 能である、このときの系列の伝搬経路を入力端子の連 続透明経路という.同様に,コアの出力端子の連続透 明性とは、その出力端子から出力される任意の長さの 系列を入力側から連続したクロックサイクルで伝搬で きる性質をいい,その伝搬経路を出力端子の連続透明 経路という.図2のコア2において,灰色の出力端子 は連続透明であり, 時刻 t-k からの連続した時刻に

コア3へのテスト系列をコア2の入力端子に印加する ことで,時刻tからの連続した時刻にその系列を出力 することが可能である、各コアに対して、テストコン トローラ (SoC 内部または外部に存在)から制御信号 が供給され、その制御信号により各コアの連続透明経 路が実現される.このように制御信号によりコアが連 続透明経路を実現している状態をコアの形状と呼ぶ. SoC の連続可検査性とは,各コア(各信号線)に対し て,他のコアの形状を選択することにより,連続透明 経路及び信号線を用いて連続テストアクセスできる性 質をいう. 図 2 では, 時刻 t からの連続した時刻にコ P3 の各入力端子へテスト系列を印加し,時刻 t+1から連続した時刻に出力される応答系列を観測するコ ア3への連続テストアクセスを示している.テストコ ントローラからの制御信号により,コア1,コア2,コ ア4の灰色の端子の連続透明経路が実現されている. コア3のテストに必要なテスト系列をSoCの外部入 力に時刻 t-l と時刻 t-k からの連続した時刻にそ れぞれ入力し、SoC の外部出力で時刻 t+1+m から の連続した時刻に出力される応答系列を観測すること でコア3の連続テストアクセスが実現される.以下, 3.1 でコアの連続透明性を , 3.2 で SoC の連続可検査 性を定義する.

# 3.1 コアの連続透明性

[定義1](コアの連続透明性) 入力端子Iのi番目のビットをI(i),出力端子Oのj番目のビットを

図 2 連続テストアクセス Fig. 2 Consecutive test access.

O(j) とする.制御入力 T により,I(i) と O(j) 間に経路 P が存在し,I(i) に連続して入力される任意の長さの系列を O(j) で連続して観測できるとき,P は連続透明経路であるといい,I(i) と O(j) は連続透明であるという.T により P を実現している状態をコアの形状という.入力端子 I( 出力端子 O )に関して,I(O) のすべてのビットを同一の T で連続透明にすることが可能であるとき,I(O) は連続透明であるといい,T により実現される経路を I(O) の連続透明経路という.すべての入出力端子が連続透明であるとき,コアは連続透明であるという.

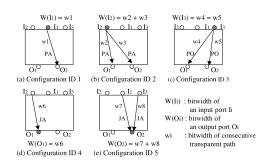

連続透明なコアとその形状を図3に示す.連続透明 なコアには様々な形状が存在し、各形状は番号によって 識別される.形状を選択することにより,各入出力端 子の連続透明経路が実現され、その端子が連続透明と なる.連続透明経路を系列の伝搬方法によって,JA型 (Justification AND), PA型(Propagation AND), PO 型 (Propagation OR)の3種類に分類する.JA 型は出力端子の連続透明経路であり、テスト系列の印 加に利用される . PA 型 , PO 型は入力端子の透明経路 であり, 応答系列の観測に利用される. 図 3(a) は PA 型の連続透明経路を示している . 入力端子  $I_1$  に入力さ れる任意の長さの系列は,出力端子 $O_2$ にのみ伝搬す る.図3(b)もPA型の連続透明経路を示しているが, 入力端子  $I_2$  に入力されるビット幅  $W(I_2)$  の任意の長 さの系列は,ビット分割し  $(W(I_2) = w2 + w3)$ ,出力 端子  $O_1$  と  $O_2$  に伝搬する  $O_3$  (c) は PO 型の連続 透明経路を示している.入力端子  $I_3$  に入力されるビッ ト幅  $W(I_3)$  の任意の長さの系列は , ファンアウトし  $(W(I_2) = w2 = w3)$ , 出力端子  $O_1$  と  $O_2$  の両方に伝 搬する . 図 3(d) は JA 型の連続透明経路を示してい

図3 連続透明なコアとその形状 Fig.3 Various configurations of a consecutive transparent core.

る.出力端子  $O_1$  から出力される任意の長さの系列は,入力端子  $I_2$  からのみ伝搬される.図 3 (e) も JA 型の連続透明経路を示しているが,出力端子  $O_2$  から出力されるビット幅  $W(O_2)$  の任意の長さの系列は,入力端子  $I_1$  と  $I_3$  から伝搬される  $(W(O_2)=w7+w8)$ .

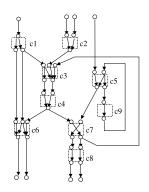

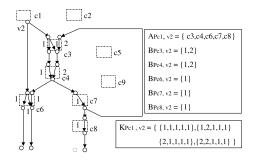

SoC の回路要素であるコアが連続透明であるとき,SoC は,外部入力,外部出力,コアの端子を頂点に対応させ,信号線,コアの連続透明経路を枝に対応させたコア接続グラフ  $G=(V,E,\lambda)$  で表現することができる.SoC に対して,コア接続グラフ  $G=(V,E,\lambda)$  を次の有向グラフ(図 4)として定義する.

•  $V = V_{PI} \cup V_{PO} \cup V_{in} \cup V_{out}$

$V_{PI}$  は  ${

m SoC}$  の外部入力に対応する頂点の集合,  $V_{PO}$  は  ${

m SoC}$  の外部出力に対応する頂点の集合,  $V_{in}$  はコアの入力端子に対応する頂点の集合,  $V_{out}$  はコアの出力端子に対応する頂点の集合とする.

•  $E = E_{core} \cup E_{net}$

$E_{core} = \{(x,y) \in V_{in} imes V_{out} \mid$ 連続透明経路に対応する枝の集合  $\}$  ,

$E_{net} = \{(y,x) \in V_{out} \times V_{in} \mid$ 信号線に対応する枝の集合  $\}$  .

•  $\lambda: E \to 2^{C \times I \times T \times W}$

C はコアの集合とする.

I は形状識別番号の集合とする.

$T = \{JA, JO, PA, PO\}$  とする.

JA,PA は連続透明経路の型を表し,PO は連続透明経路と信号線の型を表し,JO は信号線のみの型を表すラベルとする.続透明経路に対応する枝  $e\in E_{core}$ は,e の型に応じて JA,PA,PO のラベルで表される.本論文で対象とする SoC において,信号線はファ

図 4 コア接続グラフ Fig. 4 Core connectivity graph.

ンアウトのみが可能であり,テスト系列の印加と応答の観測の両方に利用することが可能である.これより,信号線  $e\in E_{net}$  は,ファンアウトのみが可能であり,テスト系列の印加に利用可能を表す JO と,連続透明経路の型である PO(ファンアウトのみが可能であり,応答の観測に利用可能)の二つのラベルで表される.W は,連続透明経路と信号線のビット幅の集合とする.

ただし, $e \in E_{net}$  ならば

$\lambda(e):\{\{\phi,\phi,JO,$ 信号線のビット幅 $\},$   $\{\phi,\phi,PO,$ 信号線のビット幅 $\}\}$

とする.

図3の連続透明経路と形状をもつコアに対する  $\lambda$  によるラベルを図5に示す.ここで,コア接続グラフ,またはその部分グラフにおいて出射枝のみをもち,入射枝をもたない頂点をソース,入射枝のみをもち,出射枝をもたない頂点をシンクとする.コアの形状を選択するとは,選択された形状識別番号をもつ枝のみを残し,他の枝をそのコアから除去することをいう.

### 3.2 SoC の連続可検査性

本論文では,コアにはテスト系列が与えられている ものと仮定し,以下の二つの条件が成り立てば SoC が 連続可検査であるとする.

- すべてのコアへの連続テストアクセスが可能

- コア間のすべての信号線のテストが可能

本節では, SoC の連続可検査性をコア接続グラフ上で 定義する. はじめに, コアの連続可制御性, 信号線の 連続可制御性, 端子の連続可観測性をコア接続グラフ 上で定義し, 次に SoC の連続可検査性を定義する.

# 3.2.1 コアの連続可制御性

コアのすべての入力端子に  $\operatorname{SoC}$  の外部入力から連続したクロックサイクルで任意の値が伝搬可能な性質としてコアの連続可制御性を次のように定義する. [ 定義 2 ]( コアの連続可制御性 )  $\operatorname{SoC}$  のコア接続グラフ G , コア  $c \in C$  について , 次の条件をすべて満

$$\begin{split} &\lambda\left(e1\right):\left\{\left\{c,2,PA,w2\right\},\left\{c,4,JA,w6\right\}\right\}\\ &\lambda\left(e2\right):\left\{\left\{c,2,PA,w3\right\}\right\}\\ &\lambda\left(e3\right):\left\{\left\{c,1,PA,w1\right\},\left\{c,5,JA,w7\right\}\right\}\\ &\lambda\left(e4\right):\left\{\left\{c,3,PO,w4\right\}\right\}\\ &\lambda\left(e5\right):\left\{\left\{c,3,PO,w5\right\},\left\{c,5,JA,w8\right\}\right\} \end{split}$$

図 5  $\lambda$  によるラベル Fig. 5 Label by  $\lambda$ .

たす無閉路コア接続部分グラフ  $G_J$  が存在するとき , コア c は連続可制御であるという . また , 部分グラフ  $G_J$  をコア c の正当化部分グラフという .

- (1)  $G_J$  のシンクは c のすべての入力端子からなり, ソースは  $\operatorname{SoC}$  の外部入力だけからなる.

- (2)  $G_J$  のすべての枝は , JA または JO のラベルをもつ .

- (3) G において,各コアに対し一つの形状を選択することで得られる部分グラフを G' とする. $G_J$  の各頂点について,

- (a) G' におけるすべての入射枝を含む.

- (b) 出射枝が *JO* のラベルをもつ場合, *G'* におけるただ一つの出射枝のみを含む. □

コア c の正当化部分グラフ  $G_J$  に存在するすべての枝は連続透明経路またはコア間を接続する信号線であり,JO または JA のラベルをもつ(条件 2)ので, $G_J$  に存在するすべての枝は SoC の実動作速度での連続したテスト系列の印加に利用可能である .c の  $G_J$  は無閉路であるので,条件 1 より,c の各入力端子に対して,SoC の外部入力から一つ以上の単純経路が存在する.更に条件 3 より,各コアは一つの形状が選択され, $G_J$  の頂点のうち  $V_{out}$  に属する頂点(コアの出力端子に対応する頂点)の連続透明性を実現するために必要なすべての入射枝(連続透明経路)が  $G_J$  に存在する.以上より,c が連続可制御であれば,c の  $G_J$  に存在する各単純経路に沿って,テスト系列を SoC の外部入力から c のすべての入力端子に連続して印加可能である.

# 3.2.2 信号線の連続可制御性

信号線に SoC の外部入力から連続したクロックサイクルで任意の値が伝搬可能な性質として信号線の連続可制御性を次のように定義する.

[ 定義 3 ](信号線の連続可制御性 ) SoC のコア接続 グラフ G , 信号線  $e=(y,x)\in E_{net}$  について,次の条件をすべて満たす無閉路コア接続部分グラフ  $G_J$  が存在するとき,信号線 e は連続可制御であるという.また,部分グラフ  $G_J$  を信号線 e の正当化部分グラフという.

- (1)  $G_J$  のシンクは y のみからなり , ソースは  $\operatorname{SoC}$  の外部入力だけからなる .

- (2)  $G_J$  のすべての枝は , JA または JO のラベルをもつ .

- (3) G において,各コアに対し一つの形状を選択することで得られる部分グラフを G' とする. $G_J$  の

各頂点について、

- (a) G' におけるすべての入射枝を含む.

- (b) 出射枝が JO のラベルをもつ場合, G' におけるただ一つの出射枝のみを含む.

コアの連続可制御性と同様に,信号線eが連続可制御であれば,eの $G_J$ に存在する各単純経路に沿って,テスト系列をSoCの外部入力からeに連続して印加可能である.

### 3.2.3 端子の連続可観測性

端子から出力される任意の系列を連続したクロックサイクルで SoC の外部出力まで伝搬可能な性質として端子の連続可観測性を次のように定義する.

[ 定義 4 ](端子の連続可観測性 ) SoC のコア接続グラフ G ,端子  $v \in V$  について ,次の条件をすべて満たす無閉路コア接続部分グラフ  $G_P$  が存在するとき ,端子 v は連続可観測であるという .また ,部分グラフ  $G_P$  を端子 v の伝搬部分グラフという .

- (1)  $G_P$  のシンクは SoC の外部出力だけからなり, ソースは端子 v のみである.

- (2)  $G_P$  のすべての枝は , PA または PO のラベルをもつ .

- (3) G において,各コアに対し一つの形状を選択することで得られる部分グラフを G' とする. $G_P$  の各頂点について,

- ( a ) 出射枝が PA のラベルをもつ場合 , G' におけるすべての出射枝を含む .

- (b) 出射枝が *PO* のラベルをもつ場合, *G'* におけるただ一つの出射枝のみを含む. □

v の  $G_P$  に存在するすべての枝は連続透明経路またはコア間を接続する信号線であり,PO または PA のラベルをもつ(条件 2)ので, $G_P$  に存在するすべての枝は SoC の実動作速度での連続したテスト応答系列の伝搬に利用可能である.c の  $G_J$  は無閉路であり,条件 1 より,v から SoC の外部出力への単純経路が存在する.条件 3 より,各コアは一つの形状が選択され, $G_P$  の頂点のうち  $V_{in}$  に属する頂点(コアの入力端子に対応する頂点)の連続透明性を実現するために必要なすべての出射枝(連続透明経路)が  $G_P$  に存在する・以上より,v が連続可観測であれば,v の  $G_P$  に存在する単純経路に沿って,v から出力される任意の応答系列を SoC の外部出力へ連続して伝搬可能である.

# **3.2.4** SoC の連続可検査の定義

コア(信号線)への連続テストアクセスを可能とするためには,連続したクロックサイクルでのテストパ

ターンの印加と出力応答の観測が同時にできなければならない.テストパターンの印加に関しては,コアのすべての入力端子に同時に連続して印加する必要があり,コアは連続可制御でなければならない.応答の観測に関しては,すべての出力端子を同時に連続して観測する必要はなく,各出力端子ごと時分割で観測すれば十分であるので,各出力端子が連続可観測であればよい.以上の理由より SoC の連続可検査性を次のように定義する.

[ 定義 5 ]( SoC の連続可検査性 ) SoC のコア接続グラフ  $G=(V,E,\lambda)$  が次の条件をすべて満たすとき , SoC は連続可検査であるという .

- ( 1 ) 各コア  $c \in C$  の各出力端子  $v \in V_{out}$  に関して,互いに共通部分をもたない c の正当化部分グラフ と v の伝搬部分グラフが存在する.

- ( 2 ) 各信号線  $e=(y,x)\in E_{net}$  に関して,互いに共通部分をもたない e の正当化部分グラフと x の伝搬部分グラフが存在する.

$\operatorname{SoC}$  が連続可検査であれば , 各コア c の各出力端子 v に関して,互いに共通部分をもたない c の正当化部 分グラフと v の伝搬部分グラフが存在する.定義 2 よ り,c の正当化部分グラフ  $G_I$  が存在すれば, $G_I$  に 存在する各単純経路に沿ってテスト系列を SoC の外部 入力から c のすべての入力端子に連続して印加可能で あり, 定義 4 より, v の伝搬部分グラフ  $G_P$  が存在す れば, $G_I$  に存在する単純経路に沿って,v から出力 される任意の応答系列を SoC の外部出力へ連続して 伝搬可能である . 更に  $G_J$  と  $G_P$  が共通部分をもた ないので,連続したクロックサイクルでのテスト系列 の印加と応答系列の観測を同時に行うことができるの で,コアへの連続テストアクセスが可能である.SoC が連続可検査であれば, 各信号線 e についても同様に 連続テストアクセスが可能となるので,コア間のすべ ての信号線のテストが可能である.

# 4. テスト容易化設計法

### 4.1 テスト 容易化設計

SoC に含まれる IP コアを設計変更することはできない.本章では,すべてのコアが連続透明であり,コア内部は設計変更できないという仮定のもとで,与えられた SoC を連続可検査にするためのテスト容易化設計法(Design for Testability,以下 DFT)を考察する.コアが連続透明でない場合,コアの入力端子から出力端子へマルチプレクサを用いてバイパス経路を

付加することにより,コア内部を設計変更することなく連続透明性を実現可能であるので,上記の仮定で一般性を失うことはない.

連続可検査な SoC は,コアの各出力端子に関して,互いに共通部分をもたない正当化部分グラフと伝搬部分グラフをもつ.更に信号線に関しても,互いに共通部分をもたない正当化部分グラフと伝搬部分グラフをもつ.これらの部分グラフの経路に沿って連続したクロックサイクルで任意の系列を伝搬することが可能である.

与えられた SoC 内のコアの出力端子,または信号線に対して,互いに共通部分をもたない正当化部分グラフと伝搬部分グラフが存在しない場合,連続可検査にするために SoC に新たに経路を付加する必要がある.この経路はマルチプレクサを用いて外部入力からの経路,または外部出力への経路を付加することで実現する.そこで,SoC を連続可検査にするための DFT を,次の最適化問題として定式化する.

[ 定義 6 ]( 連続可検査 DFT ) SoC を連続可検査にするための DFT を次の最適化問題として定義する.

- ・入力:SoC(コア接続グラフ)

- ・出力:連続可検査な SoC

- ・ 最適化目標:付加するハードウェア量最小化 □

- 4.2 テスト容易化設計法

連続可検査 DFT を解くための発見的アルゴリズムを示す. 本アルゴリズムでは,連続可検査 DFT を解くために以下の四つの段階に分けて考える.

- (1) コアの連続可制御性のための DFT

- (2) コアの連続可観測性のための DFT

- (3) 信号線の連続可制御性のための DFT

- (4) 信号線の連続可観測性のための DFT

各段階で最適解を求めるアルゴリズムを以下に示す.

**4.2.1** コアの連続可制御性のための DFT

具体的には以下の方法で各コアに対して制御初期グラフ,制御中間グラフを生成する.その制御中間グラフが正当化部分グラフとなるための条件式を導出し,整数計画問題を解くことで最小の付加ハードウェアですべてのコアを連続可制御とする.

### [Step1] 制御初期グラフの生成

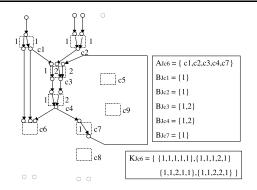

コア接続グラフ G から , コア  $c\in C$  の制御初期グラフ  $G_{J_c}$  を以下の方法で生成する . 図 6 に , 図 4 のコア接続グラフ G に対する , コア c6 の制御初期グラフ  $G_{J_{c6}}$  を示す . 図中の数字は , その連続透明経路を実現するための形状識別番号を表す .

図 6 制御初期グラフ  $G_{J_{c6}}$  Fig. 6 Justification initial graph.

はじめに,G から JA または JO のラベルをもつ枝のみを残し,他の枝を除去する.次に,c 内の連続透明経路の枝を G から除去し,c の入力端子に対応する頂点  $v\in V_{in}$  をすべてをシンクとする.そのシンクから有向辺を逆にたどることで到達可能となる枝,頂点を c の制御初期グラフ  $G_{J_c}$  とする. $G_{J_c}$  には c の入力端子に対応する頂点も含む.

$G_{J_c}$  に含まれるコアの集合を  $A_{J_c}$  とする.ここでコアが  $G_{J_c}$  に含まれるとは,コアに属する一つ以上の連続透明経路が  $G_{J_c}$  に存在することをいう.コア $a\in A_{J_c}$  に対し, $G_{J_c}$  に含まれる形状の集合を  $B_{J_a}$  とする. $a\in A_{J_c}$  に対する  $B_{J_a}$  の直積集合を

$$K_{J_c} = \prod_{a \in A_{J_c}} B_{J_a}$$

$$= B_{J_{a1}} \times B_{J_{a2}} \times B_{J_{a3}} \times \dots$$

とする.制御初期グラフでは,各コアには複数の形状 識別番号が存在し,連続透明性が実現されていない. [Step2] 制御中間グラフの生成

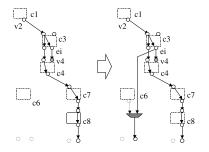

$G_{J_c}$  と  $k\in K_{J_c}$  から,c の制御中間グラフ  $G_{J_{c,k}}$  を以下の方法で生成する.図 7 に,図 6 の  $G_{J_{c6}}$  に対する,制御中間グラフ  $G_{J_{c6,k1}}$  を示す.図中の JA,JO は連続透明経路及び信号線の型を表す.

はじめに, $A_{J_c}$  に属するコアにおいて,k に対応する形状をそれぞれ選択し,各コアの連続透明性を実現する.このとき,新たにシンクとなった頂点からのみ到達可能な枝,頂点を  $G_{J_c}$  から除去することで得られるグラフを制御中間グラフ  $G_{J_{c,k}}$  とする. $G_{J_{c,k}}$  はG に対し,各頂点はすべての入射枝を含み,各コアについて一つの形状に関する枝のみを残した部分グラフである. $G_{J_{c,k}}$  の頂点のうち,以下のいずれかの条件

図 7 制御中間グラフ  $G_{J_{c6,k1}}$  Fig. 7 Justification middle graph.

に当てはまる頂点 q の集合を  $Q_J$  とする.

- (1) q はソースであり,  $V_{PI}$  に属さない

- (2) q は JO のラベルをもつ二つ以上の出射枝をもつ

- (3) q を含む閉路が存在

$Q_J$  は  $G_{J_{c,k}}$  の頂点の中で,正当化部分グラフの条件 ([ 定義 2 ])にあてはまらない頂点の集合となる.

[Step3] 整数計画問題への帰着

コアcの連続可制御性の評価変数として,以下の整数変数を定義する.

$Y_c$ : c に関する連続可制御性

$Y_{c,k}$ : c の形状集合 k に関する連続可制御性

$Y_{c,k}^q$ :  $G_{J_{c,k}}$  における頂点 q に関する

連続可制御性

各変数は 1 以上のとき,その性質を満たすものとする. 更に, $x_{e_i}$  を次のように定義する.

$$x_{e_i} = egin{cases} 1 & e_i \ ext{c} \ ext{c} \ ext{v} \ ext{J} \ ext{L} \ ext{J} \ ext{L} \ ext{D} \ ext{D} \ ext{T} \ ext{D} \ ext{D} \ ext{T} \ ext{D} \ ext{D} \ ext{T} \ ext{D} \$$

この  $e_i$  を用いて  $Y^q_{c,k}$  を q が満たす条件によって,以下の( 1 )~( 3 )のように定義する .q が( 1 )~( 3 )の複数の条件を同時に満たす場合は,各条件で定義される  $Y^q_{c,k}$  の積を q の  $Y^q_{c,k}$  として定義する.

(1) q が  $G_{J_{c,k}}$  のソースであり , $V_{PI}$  に属さない 場合

q と  $G_{J_{c,k}}$  のシンク間の単純経路の集合を S とする .q に関して  $G_{J_{c,k}}$  を連続可制御とするためには,S に属する各単純経路 s に対して,一つ以上の信号線にマルチプレクサを付加し,SoC の外部入力からの経路を実現すれば十分である .s に存在する信号線に対応する枝の集合を  $E_s$  とすると .s に対し,一つ以上

の信号線にマルチプレクサを付加するとは,以下の式で表される $m_s$ が1以上となることをいう.

$$m_s = \sum_{e_i \in E_s} x_{e_i} \tag{2}$$

この  $m_s$  を用いて ,  $Y_{c,k}^q$  を次の式で表現する .

$$Y_{c,k}^q = \prod_{s \in S} m_s \tag{3}$$

# (2) q が JO のラベルをもつ二つ以上の出射枝をもつ場合

$G_{J_{c,k}}$  における q の出射枝の集合を R とする . q と  $G_{J_{c,k}}$  のシンク間の単純経路の集合のうち, $r \in R$  を含む単純経路の集合を  $S_r$  とする . 正当化部分グラフでは,頂点に対して一つの JO のラベルをもつ出射枝のみを含む([定義 2]). q に関して  $G_{J_{c,k}}$  を連続可制御とするためには,R-r の各要素  $r_n$  に対する  $S_{r_n}$  の各単純経路に対して,一つ以上の信号線にマルチプレクサを付加し,SoC の外部入力からの経路を実現すれば十分である. $m_s$  を用いて, $Y_{c,k}^q$  を次の式で表現する.

$$Y_{c,k}^{q} = \sum_{r \in R} \left( \prod_{r_n \in R-r} \left( \prod_{s \in S_{r_n}} m_s \right) \right) \tag{4}$$

# (3) q を含む閉路が存在する場合

$G_{J_{c,k}}$  において,q を含む閉路の集合を S とする.q に関して  $G_{J_{c,k}}$  を連続可制御とするためには,S に属する各閉路 s に対し,一つ以上の信号線にマルチプレクサを付加し, $\mathrm{SoC}$  の外部入力からの経路を実現すれば十分である. $m_s$  を用いて, $Y_{c,k}^q$  を次の式で表現する.

$$Y_{c,k}^q = \prod_{s \in S} m_s \tag{5}$$

次に  $Y_{c,k}$  について考える. $Q_J=\phi$  のとき, $G_{J_{c,k}}$  は正当化部分グラフである. $Q_J \neq \phi$  のとき, $Q_J$  のすべての要素に関して  $G_{J_{c,k}}$  を連続可制御とすれば, $G_{J_{c,k}}$  は正当化部分グラフとなる.これより, $Y_{c,k}$  は  $Y_{c,k}^q$  を用いることで以下の式で表現できる.

$$Y_{c,k} = \begin{cases} \prod_{q \in Q_J} Y_{c,k}^q & (Q_J \neq \phi \text{ のとき}) \\ 1 & (Q_J = \phi \text{ のとき}) \end{cases}$$

(6)

次に  $Y_c$  について考える . c が連続可制御であるとは ,  $K_{J_c}$  の一つ以上の要素に対して連続可制御であること

をいう . これより ,  $Y_c$  は  $Y_{c,k}$  を用いることで以下の式で表現できる .

$$Y_c = \sum_{k \in K_{I_c}} Y_{c,k} \tag{7}$$

以上より, すべてのコアが連続可制御であるための必要十分条件は

$$\prod_{c \in C} Y_c \ge 1 \tag{8}$$

となる.連続可検査 DFT の最適化目標は,付加する ハードウェア量最小である.これは,マルチプレクサ が付加される信号線のビットの合計を最小化すること と等価であるので,以下の関数で表現することがで きる.

$$\sum_{e_i \in E_{net}} x_{e_i} \cdot width(e_i) \tag{9}$$

ただし, $width(e_i)$ は信号線 $e_i$ のビット幅を表す.

コアの連続可制御性のための DFT は,条件式 (8),目的関数 (9) とする整数計画問題に帰着することができる.この式 (8),(9) で表現される整数計画問題を解くことで,マルチプレクサを付加すべき信号線の集合が得られる.この集合の各要素  $e_i$  に対して,図 8 のようにマルチプレクサを用いて,外部入力からの経路を実現することで,最小のハードウェア量ですべてのコアを連続可制御にすることができる.

### **4.2.2** コアの連続可観測性のための DFT

具体的には以下の方法で各コアに対して伝搬初期グラフ,伝搬中間グラフ,伝搬中間部分グラフを生成する.その伝搬中間部分グラフが伝搬部分グラフとなるための条件式を導出し,整数計画問題を解くことで,

図 8 連続可制御性のためのマルチプレクサ Fig. 8 Insert of multiplexer for consecutive controllability.

最小の付加ハードウェアですべてのコアを連続可観測 とする.

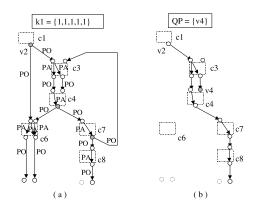

### [Step1] 伝搬初期グラフの生成

コア接続グラフ G から , コア  $c\in C$  の出力端子  $o\in V_{out}$  に関する伝搬初期グラフ  $G_{Pc,o}$  を以下の方法で生成する . 図 9 に , 図 4 のコア接続グラフ G に対する , コア c1 の出力端子 v2 に関する伝搬初期グラフ  $G_{Pc1,v2}$  を示す .

はじめに,G から c の正当化部分グラフ  $G_{J_c}$  を除去する.更に,G から PA または PO のラベルをもつ枝のみを残し,他の枝を除去する.次に,c 内の連続透明経路の枝を G から除去し,o をソースとする.そのソースから有向辺をたどることで到達可能となる枝,頂点の集合を c の o に関する伝搬初期グラフ  $G_{Pc,o}$  とする. $G_{Pc,o}$  に o も含む.

$G_{Pc,o}$  に含まれるコアの集合を  $A_{Pc,o}$  とする.コア  $a\in A_{Pc,o}$  に対し, $G_{Pc,o}$  に含まれる形状の集合を $B_{Pa}$  とする. $a\in A_{Pc,o}$  に対する  $B_{Pa}$  の直積集合を

$$K_{P_{c,o}} = \prod_{a \in A_{P_{c,o}}} B_{P_{a1}}$$

$$= B_{P_{a1}} \times B_{P_{a2}} \times B_{P_{a3}} \times \dots$$

とする.伝搬初期グラフでは,各コアには複数の形状識別番号が存在し,連続透明性が実現されていない. [Step2] 伝搬中間グラフの生成

$G_{Pc,o}$  と  $k\in K_{Pc,o}$  から , c の o に関する伝搬中間グラフ  $G_{Pc,o,k}$  を以下の方法で生成する . 図 10 に , 図 9 の  $G_{Pc1,v2}$  に対する , 伝搬中間グラフ  $G_{Pc1,v2,k1}$  を示す .

はじめに, $A_{Pc,o}$  に属するコアにおいて,k に対応する形状を選択し,各コアの連続透明性を実現する.このとき,新たにソースとなった頂点からのみ到達可

図 9 伝搬初期グラフ  $G_{P_{c1,v2}}$  Fig. 9 Propagation initial graph.

能な枝,頂点を  $G_{P_{c,o}}$  から除去することで得られるグラフを伝搬中間グラフ  $G_{P_{c,o,k}}$  とする .  $G_{P_{c,o,k}}$  は G に対し,各頂点はすべての入射枝を含み,各コアについて一つの形状に関する枝のみを残した部分グラフである。

## [Step3] 伝搬中間部分グラフの生成

$G_{P_{c,o,k}}$  に対し,各頂点が PO のラベルをもつ出射 枝をただ一つもつという条件のもとで,o から到達可能な枝,頂点からなる部分グラフ  $G_{P_{c,o,k}}^f$  を伝搬中間部分グラフとし,伝搬中間部分グラフの集合を  $G_{P_{c,o,k}}^F$  には PO のラベルをもつ出射枝を二つ以上もつ頂点は存在しない.図 10 (a) に対する  $G_{P_{c,v,k}}^f$  を図 10 (b) に示す.

$G^{f}_{P_{c,o,k}}$  のうち,以下のいずれかの条件に当てはまる頂点 q の集合を  $Q_P$  とする.

- (1) q はシンクであり,  $V_{PO}$  に属さない

- (2) q を含む閉路が存在

$Q_P$  は  $G^f_{P_{c,o,k}}$  の頂点の中で,伝搬部分グラフの条件 ([ 定義 4 ]) にあてはまらない頂点の集合となる.

### [Step4] 整数計画問題への帰着

コア c の出力端子 o に関する連続可観測性の評価変数として,以下の整数変数を定義する.

$Z_{c,o}$  : c の o に関する連続可観測性  $Z_{c,o,k}$  : c の o の形状集合 k に関する

連続可観測性

$Z^{f,q}_{c,o,k}:\,G^f_{P_{c,o,k}}$  における頂点 q に関する

連続可観測性

各変数は1以上のとき,その性質を満たすものとする.

☑ 10 (a)  $G_{P_{c1,v2,k1}}$ , (b)  $G_{P_{c1,v2,k1}}^f$ Fig. 10 Propagation middle graph.

式 (2) を用いて  $Z^{f,q}_{c,o,k}$  を q が満たす条件によって,以下の (1),(2) ように定義する .q が (1),(2) の条件を同時に満たす場合は,各条件で定義される  $Y^q_{c,k}$  の積を q の  $Y^q_{c,k}$  として定義する.

(1) q が  $G^f_{P_{c,o,k}}$  のシンクであり ,  $V_{PO}$  に属さない場合

q と o 間の単純経路の集合を S とする .q に関して  $G^f_{P_{C,o,k}}$  を連続可観測とするためには,S に属する各 単純経路 s に対して,s の一つ以上の信号線から SoC の外部出力までの経路をマルチプレクサを用いて実現 すれば十分である .s に存在する信号線に対応する枝の集合を  $E_s$  とすると,s に対し,一つ以上の信号線 から SoC の外部出力までの経路をマルチプレクサを 用いて実現するとは,以下の式で表される  $m_s'$  が 1 以上となることをいう.

$$m_s' = \sum_{e_i \in E_s} x_{e_i} \tag{10}$$

この  $m_s'$  を用いて, $Y_{c,k}^q$  を次の式で表現する. $m_s'$  を用いて, $Z_{c,o,k}^{f,q}$  を次の式で表現する.

$$Z_{c,o,k}^{f,q} = \prod_{s \in S} m_s' \tag{11}$$

# (2) qを含む閉路が存在する場合

$G^f_{P_{c,o,k}}$  において,q を含む閉路の集合を S とする.q に関して  $G^f_{P_{c,o,k}}$  を連続可観測とするためには,S に属する各閉路 s に対し,一つ以上の信号線から SoC の外部出力への経路をマルチプレクサを用いて実現すれば十分である. $m_s'$  を用いて, $Z^{f,q}_{c,o,k}$  を次の式で表現する.

$$Z_{c,o,k}^{f,q} = \prod_{s \in S} m_s' \tag{12}$$

次に  $Z^f_{c,o,k}$  について考える  $.Q_P=\phi$  のとき, $G^f_{P_{c,o,k}}$  は伝搬部分グラフである  $.Q_P \neq \phi$  のとき, $Q_P$  のすべての要素に関して  $G^f_{P_{c,o,k}}$  を連続可観測とすれば, $G^f_{P_{c,o,k}}$  は伝搬部分グラフとなる.これより, $Z^f_{c,o,k}$  は  $Z^{f,q}_{c,o,k}$  を用いることで以下の式で表現できる

$G^F_{P_{c,o,k}}$  に属する一つ以上の  $G^f_{P_{c,o,k}}$  に関して連続可観測であれば ,  $G_{P_{c,o,k}}$  は連続可観測である . これ

より, $Z_{c,o,k}$  は  $Z_{c,o,k}^f$  を用いることで以下の式で表現できる.

$$Z_{c,o,k} = \sum_{G_{P_{c,o,k}}^f \in G_{P_{c,o,k}}^F} Z_{c,o,k}^f$$

(14)

次に  $Z_{c,o}$  について考える .c の o が連続可観測であるとは  $,K_{P_{c,o}}$  の一つ以上の要素に対して連続可観測であることをいう . これより  $,Z_{c,o}$  は  $Z_{c,o,k}$  を用いることで以下の式で表現できる .

$$Z_{c,o} = \sum_{k \in K_{P_{c,o}}} Z_{c,o,k} \tag{15}$$

コア c の出力端子に対応する頂点の集合を  $O_c$  とすると , すべてのコアが連続可観測であるための必要十分条件は

$$\prod_{c \in C} \left( \prod_{o \in O_c} Z_{c,o} \right) \ge 1 \tag{16}$$

となる.連続可検査 DFT の最適化目標は,付加する ハードウェア量最小である.これは,マルチプレクサ を用いて SoC の外部出力までの経路を実現すべき信 号線のビットの合計を最小化することと等価であるの で,以下の関数で表現することができる.

$$\sum_{e_i \in E_{net}} x_{e_i} \cdot width(e_i) \tag{17}$$

ただし, $width(e_i)$ は信号線 $e_i$ のビット幅を表す.

コアの連続可観測性のための DFT は , 条件式 (16) , 目的関数 (17) とする整数計画問題に帰着することができる.この式 (16) , (17) で表現される整数計画問題を解くことで,マルチプレクサを用いて外部出力への経路を付加すべき信号線の集合が得られる.この集合

図 11 連続可観測性のためのマルチプレクサ Fig. 11 Insert of multiplexer for consecutive obserbability.

の各要素  $e_i$  に対して,図 11 のようにマルチプレクサを用いて,外部出力への経路を実現することで,最小のハードウェア量ですべてのコアを連続可観測にすることができる.

4.2.3 信号線の連続可制御性,連続可観測性のための DFT

連続可制御性のための DFT は **4.2.1**, 連続可観測性のための DFT は **4.2.2** と同様の手続きで行うことができる.

# 5. む す び

本論文では連続可検査性に基づく SoC のテスト容易化設計法を提案した・本論文で提案した連続可検査性を満たす SoC は,すべてのコアとすべての信号線に対する連続テストアクセスが可能である.これにより,各コアに提供される任意のテスト系列を SoC の外部入力から実動作速度で連続してコアへ印加し,その応答を SoC の外部出力で連続して観測することが可能となり,コア単体に対してテスト可能な故障は,SoC に組み込まれた後でもテスト可能であることが保証できる.信号線も同様に,任意のテスト系列を実動作速度で連続して SoC 外部入力から印加し,その応答を SoC の外部出力で連続して観測することが可能である.

コアの入力端子から出力端子へマルチプレクサを用いてバイパス経路を付加することにより,コア内部を変更することなく連続透明性を実現可能であるが,各端子ごとにマルチプレクサが必要となり,面積オーバヘッドが大きくなる.今後の課題としては,コアの内部構造や通常動作を利用し,低い面積オーバヘッドで連続透明性を実現するコアに対するテスト容易化設計法の開発が挙げられる.また,本論文ではコアのテスト方式として外部テスト方式のみを対象としたが,組込み自己テスト可能なコアを含む場合への拡張も今後の課題である.

謝辞 本研究に際し,多くの貴重な意見を頂いた大阪大学の増澤利光教授,本学の井上美智子助教授,大竹哲史助手はじめ情報論理学講座の諸氏に深く感謝します.本研究は一部,奈良先端科学技術大学院大学支援財団教育研究活動支援による研究助成,及び新エネルギー・産業技術総合開発機構(NEDO)から半導体理工学研究センター(STARC)に委託された「SoC先端設計技術の研究開発」の一部として奈良先端科学技術大学院大学に再委託され実施されています.

#### 瀬 文

- Y. Zorian, E.J. Marinissen, and S. Dey, "Testing embedded-core based system chips," Proc. 1998 Int. Test Conf., pp.130–143, Oct. 1998.

- [2] S. Bhatia, T. Gheewala, and P. Varma, "A unifying methodology for intellectual property and custom logic testing," Proc. 1996 Int. Test Conf., pp.639–648, Oct. 1996.

- [3] T. Ono, K. Wakui, H. Hikima, Y. Nakamura, and M. Yoshida, "Integrated and automated design-fortestability implementation for cell-based ICs," Proc. 6th Asian Test Symp., pp.122–125, Nov. 1997.

- [4] N.A. Touba and B. Pouya, "Testing embedded cores using partial isolation rings," Proc. 15th VLSI Test Symp., pp.10–16, May 1997.

- [5] L. Whetsel, "An IEEE 1149.1 based test access architecture for ICs with embedded cores," Proc. 1997

Int. Test Conf., pp.69–78, Nov. 1997.

- [6] M. Nourani and C.A. Papachristou, "Structural fault testing of embedded cores using pipelining," Journal of Electronic Testing: Theory and Applications 15, pp.129–144, 1999.

- [7] I. Ghosh, N.K. Jha, and S. Dey, "A low overhead design for testability and test generation technique for core-based systems-on-a-chip," IEEE Trans. CAD, vol.18, no.11, p.1661, Nov. 1999.

- [8] I. Ghosh, S. Dey, and N.K. Jha, "A fast and low cost testing technique for core-based system-onchip," Proc. 35th Design Automation Conf., pp.542– 547, June 1998.

(平成13年5月2日受付,9月4日再受付)

# 米田 友和 (学生員)

平 10 阪大・工・情報システム卒 . 平 13 奈良先端科学技術大学院大学博士前期課程 了 . 現在 , 同博士後期課程に在学中 . 現在 , テスト容易化設計の研究に従事 .

# 藤原 秀雄 (正員:フェロー)

昭 44 阪大・工・電子卒 . 昭 49 同大大学院博士課程了 . 同大・工・電子助手 , 明治大・工・電子動手 , 明治大・工・電子通信助教授 , 情報科学教授を経て , 現在奈良先端大・情報科学教授 . 昭 56 ウォータールー大客員助教授 . 昭 59 マッギル大客員準教授 . 論理設計論 , フォールト

トレランス,設計自動化,テスト容易化設計,テスト生成,並列処理,計算複雑度に関する研究に従事.著書「Logic Testing and Design for Testability」(MIT Press)など.大川出版賞、IEEE Computer Society Meritorious Service Award.情報処理学会会員,IEEE Computer Society Golden Core Member,IEEE Fellow.