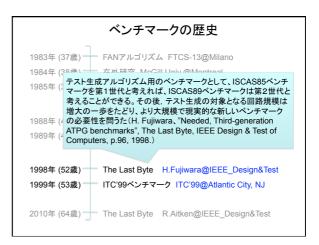

In 1983 I published the FAN algorithm, and by using actual combinational circuits, showed its superiority over both the D-algorithm (by J.P. Roth) and the the Dalgorithm (by J.P. Roth) and the PODEM algorithm (by P. Goel). In 1984 I discussed ATPG (automatic rest patern generation) benchmarking with Franc Brglez (then with Bell Northern Research and now with North Carolina State University) while I was on sabbatical visiting Vinod Agarwal at McGill University.

batical visiting Vinod Aşarwal at McGill University.

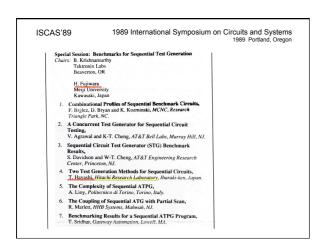

Before this, we had no benchmarks for ATPG algorithms. Brglez and agreed that benchmark circuits helped advance ATPG algorithm research and development. We organized a special session on combinational ATPG henchmarking at ISCAS 85 (the 1985 International Symposium on Circuits and Systems) in Kyoto, Japan. With the cooperation of many people from cooperation of many people from industry and universities in the USA, Canada, Europe, and Japan, we col-lected excellent benchmarks with var-ious and useful characteristics.

Later, others reported many better, more-efficient ATPG algorithms for combinational circuits. The wide-spread availability of these benchmarks drove the development of new algorithms, as researchers strove to generate the best-known results in terms of runtime, vector length, and

Today, new benchmarks are required again. The existing ISCAS 85/89 benchmarks are no longer close to the size of industrial designs. We need much larger circuits (perhaps several million gates) to realistically study. ATPG efficiency. We need circuits with features found in modern designs and not found in the current benchmarks. We encourage the development of advanced ATPG algorithms that can achieve almost 100% fault efficiency for very large, realistic circuits within prac-

tical computation time.

The current benchmarks are described in a simple netlist format. Future benchmarks should be available at the behavioral, register-transfer, and gate levels. They should be described in a high-level language such as VHDL to facilitate research on high-level ATPG.

> The ISCAS 85 benchmarks were firstgeneration benchmarks for ATPG algo-rithms, and the ISCAS 89 benchmarks were the second generation. We now need a third generation to tackle urgent current issues and continue to stimu late research on solutions for future issues. Perhaps the solutions to the impossible challenges of today, when represented in third-generation bench-marks, will become the new products of tomorrow.